CXL controller IP

Filter

Compare

84

IP

from

13

vendors

(1

-

10)

-

CXL Controller

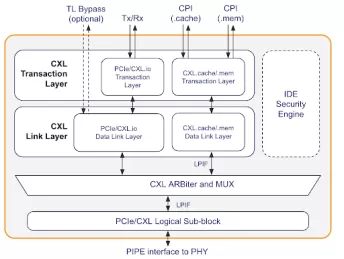

- Compliant with CXL Specification version 2.0/1.1 and PCIe Base Specification 5.0 (32 Gbps per lane)

- Complaint with PIPE 5.x interface

- Supports X16, X8, X4, X2 and X1 lane widths

- Supports 512, 256 and 128 Data path widths

- Supports PCI Express Alternate Protocol

-

CXL Controller IP

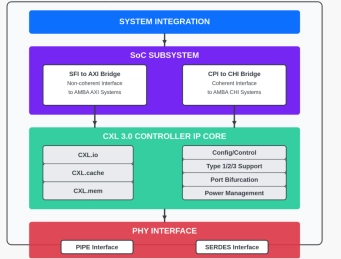

- The CXL/PCIe Controller IP carries out CXL 3.0 specification and is backward compatible to CXL 2.0 and 1.1.

- Possessing high customizability and supportability, this controller provides a comprehensive CXL solution.

-

CXL CONTROLLER IIP

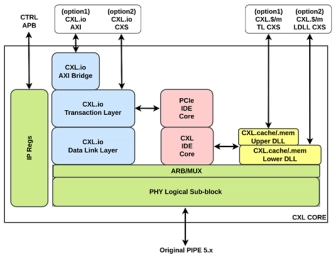

- Compliant with CXL 1.0/1.1 Specifications

- Supports Native PCIe mode and below features as defined in the PCIe specification

- PCIE Express specs 1.0/2.0/3.0/4.0/5.0

- PIPE interface

-

CXL 3.0 Controller

- The CXL Controller IP is micro-architected with power, performance, and area optimization for high bandwidth, minimum latency, and low power applications.

- The CXL IP supports seamless transition from FPGA prototyping to production silicon implementation.

- Featuring native integration with SignatureIP's Coherent and Non-coherent Network-on-Chip (NoC) IPs, this controller enables robust SoC subsystems and complete platform solutions

-

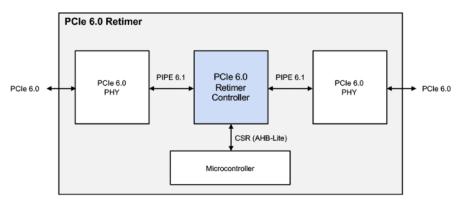

PCIe 6.0 Retimer Controller with CXL Support

- Designed to the latest PCI Express 6.0 (64 GT/s), and capable of supporting 32.0, 16.0, 8.0, 5.0 and 2.5 GT/s link rates

- Supports x1, x2, x4, x8 and x16 link widths

- CXL aware and supports sync header bypass

- Supports PIPE 5.2/6.1 compatible PHYs

- Optimized data-path for low latency insertion

-

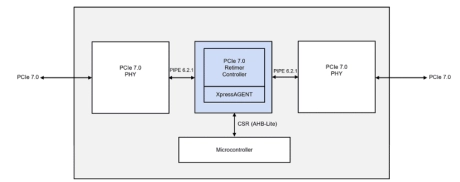

PCIe 7.0 Retimer Controller with CXL Support

- Supports PCIe 7.0 128 GT/s speeds at up to x16 lanes

- CXL 3.0 aware

- Supports PIPE 6.2.1 compatible PHYs

- Optimized for low latency

- Highly-configurable equalization algorithms and adaptive behaviors

-

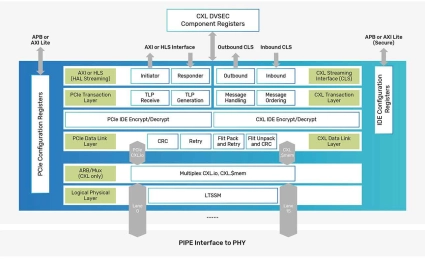

CXL 3.1 Controller

- Ultra-low Transmit and Receive latency

- Internal data path size automatically scales up or down (256, 512 or 1024 bits) based on max. link speed and width for optimal throughput

- Supports backwards compatibility to PCIe 6.1

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Optional QuickBoot mode allows for up to 4x faster link training, cutting system-level simulation time by 20%

- Loopback Mode support at DLL for CXL.mem and CXL.cache protocols

- Merged Replay and Transmit buffer enables lower memory footprint

-

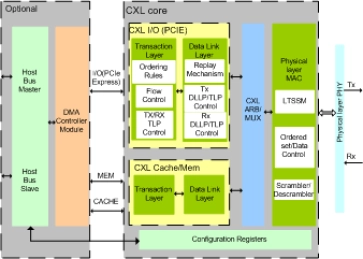

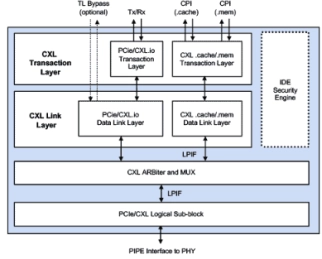

Controller for CXL

- The Controller IP for CXL provides the logic required to integrate a root-port (RP), end-point (EP), or dual-mode (DM) controller into any system on chip (SoC), and supports CXL 3.1, CXL 2.0 and CXL 1.1

- Designed for lowest latency at the highest bandwidth possible and with a rich set of client interfaces available, the Cadence Controller IP for CXL allows superior flexibility for all three device types in the CXL specification

- The Controller IP for CXL has been robustly verified with lead OEM partners in pre-silicon, and the Cadence subsystem test chips for PCIe and CXL include a CXL controller

-

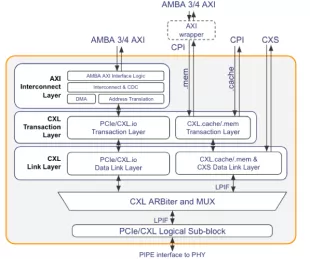

CXL 2.0 Controller with AXI

- Internal data path size automatically scales up or down (256-, 512- bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

-

CXL 2.0 Controller

- Internal data path size automatically scales up or down (256, 512 bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs (when supported)