CSI-2 Controller IP

Filter

Compare

286

IP

from

16

vendors

(1

-

10)

-

MIPI CSI-2 Controller Core

- Fully MIPI CSI-2 standard compliant

- 64 and 32-bit core widths

- Transmit and Receive versions

- Supports 1-8, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

-

MIPI CSI-2 Host Controller

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats

-

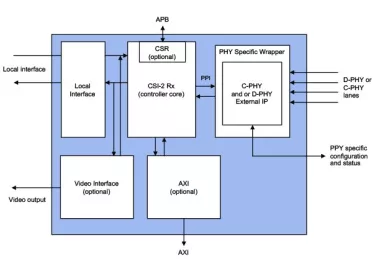

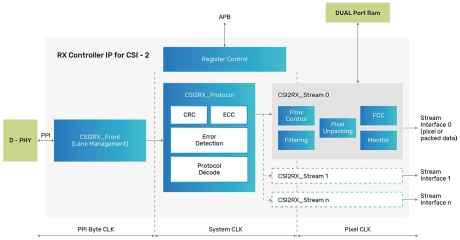

MIPI CSI-2 RX Controller

- Lane merging, virtual channel detection, and programmable data extraction

- Error detection and correction, including packet-level and protocol decoding errors

- Supports all pixel formats defined in the CSI-2 standard

-

MIPI CSI-2 RX Controller Subsystem

- Support for 1 to 4 PPI Lanes

- Line rates ranging from 80 to 1500 Mb/s

- Multiple data type support (RAW,RGG,YUV)

- AXI IIC support for CCI interface

-

MIPI CSI-2 TX Controller

- Standards Compliance. CSI-2 v2.1, with 8-bit PPI data width and links with 1, 2, or 4 data lanes

- Provides up to 4 Independent Stream Output Interfaces, allowing a highly configurable range of options, including multiple pixel modes, various buffering modes, packed data mode, Data Type selection, and Virtual Channel or Data Type interleaving

-

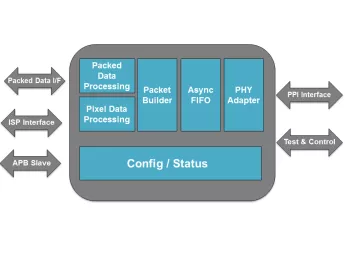

MIPI CSI2 Transmit Controller

- Camera Serial Interface (CSI-2) version 1.1

- D-PHY version 1.1

- CSI-2 interface on device side supports

- AMBA APB Slave for Control and Status

-

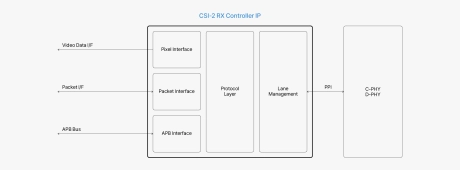

MIPI CSI-2 RX Controller

- Standards Compliant. CSI-2 v2.1, with 8-bit and 16-bit PPI data width and links with 1, 2, 4, or 8 data lanes

- Provides up to 8 Independent Stream Output Interfaces, allowing a highly configurable range of options, including multiple pixel modes, various buffering modes, packed data mode, Data Type selection, and Virtual Channel or Data Type interleaving

-

MIPI CSI-2 V4 Host Controller Stnd

- Supports key features of the latest MIPI CSI-2 specification

- PPI interface to MIPI C-PHY v1.2 and D-PHY v2.1

- Programmable multi-lane merging

- Short and long packet format and all primary and secondary CSI-2 data formats