5G DSP IP

Filter

Compare

12

IP

from

4

vendors

(1

-

10)

-

5G IoT DSP

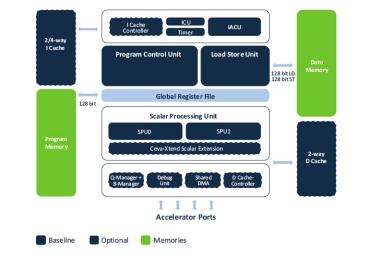

- The XC21 is the most efficient vector DSP core available today for communications applications.

- The XC21 DSP is designed for low-power, cost- and size-optimized cellular IoT modems, NTN VSAT terminals, eMBB and uRLLC applications.

- Ceva-XC21 offers scalable architecture and dual thread design with support for AI, addressing growing demand for smarter, yet more cost and power efficient cellular devices

-

5G RAN DSP

- The XC23 is the most powerful DSP core available today for communications applications. The-XC23 offers scalable architecture and dual thread design with support for AI, addressing growing demand for smarter, more efficient wireless infrastructure

- Targeted for 5G and 5G-Advanced workloads, the XC23 has two independent execution threads and a dynamic scheduled vector-processor, providing not only unprecedented processing power but unprecedented utilization on real-world 5G multitasking workloads.

-

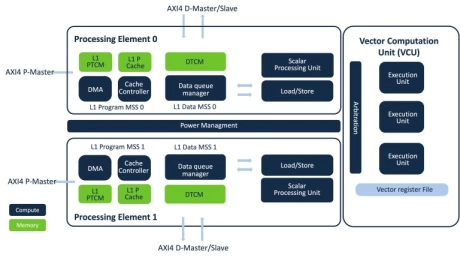

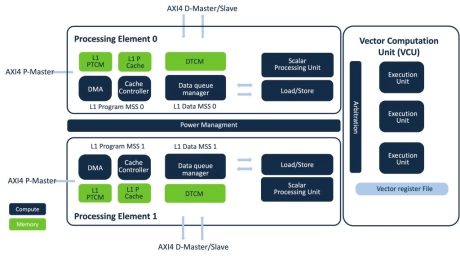

Scalable 5G modem platform

- The PentaG2 is a complete IP platform for implementing a wide range of user-equipment and IoT cellular modems.

- The platform includes a variety of DSPs, modem hardware modules, software libraries, and simulation tools.

- Capabilities of the PentaG2 include New Radio (NR) physical layer design ranging across all 3GPP profiles from RedCap IoT and mMTC, through eMBB up to ultra-reliable low-latency communications (URLLC).

-

Software Defined Radio for high end 4G/ 5G and large MIMO application

- 8x8 Transmit and Receive Antennas support

- TI Multi-core communication processor, 1.2 GHz

- 8 C66X DSP cores and 4 ARM cores

- NOR flash – 32MB, NAND Flash – 512MB

-

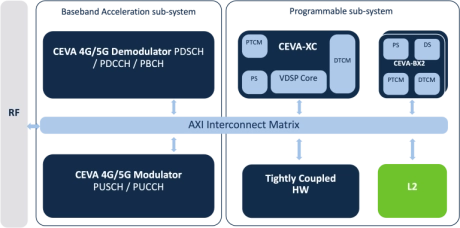

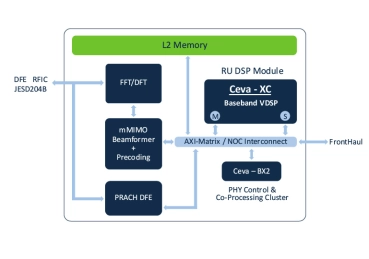

Open RAN Platform for Base Station and Radio

- The Ceva-PentaG RAN platform is a modular, optimized hardware and software IP for implementing L1 PHY baseband processing in 5G base station and other cellular infrastructure SoCs.

- Employing Ceva’s highest-performance DSP cores and dedicated hardware accelerators teamed with optimized software, the Ceva-PentaG RAN platform is in use by 5G industry incumbents, and can substantially reduce development time and risk for new entrants.

-

112G-ULR PAM4 SerDes PHY

- Supports full-duplex 1.25Gbps to 112.5Gbps data rates

- Superior bit error rate (BER) performance across high-loss and reflective channels

- Compliant with IEEE 802.3ck and OIF standard electrical specifications

- Supports flexible SoC floorplan and IP placement and provides package substrate guideline/reference designs

-

56G-LR Pam4 SerDes PHY

- Supports Ethernet, FC, CPRI, and eCPRI protocols

- Compliant to IEEE 802.3ck and OIF standard electrical specifications

- Supports 56Gbps PAM4 and 28G, 10G, and sub-10Gbps NRZ data rates

- Unique firmware-controlled adaptive power design provides optimal power and performance tradeoffs and more efficient system designs based on platform requirements

- Continuous calibration and adaption provide robust performance across process, voltage, and temperature

- Supports industrial temperature range -40°C – 125°C

-

Baseband processor

- The Ceva-BX2 baseband processor IP handles both signal-processing and control workloads with up to 16 GMACs per second performance and high-level-language programming.

- It supports a range of integer and floating-point data types for a wide range of baseband applications like 5G PHY control, and exploits a high degree of parallelism, but with remarkably compact code size.

- Optimized high-speed interfaces expedite connection to other Ceva cores or to accelerators.

-

Narrow band - IoT Release-14 UE PHY. (L1) IP

- 3GPP Rel-14 Cat-NB UE Solution

- FDD Support

- Single Antenna Tx and Rx

- 200 KHz Bandwidth

-

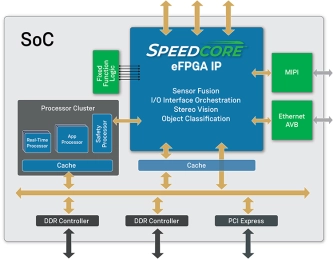

Embedded FPGA

- Speedcore embedded FPGA (eFPGA) IP has brought the performance and flexibility of programmable logic to ASICs and SoCs.

- Customers can integrate a Speedcore eFPGA IP into an ASIC or SoC for high-performance, compute-intensive and real-time processing applications such as artificial intelligence (AI), machine learning (ML), 5G wireless, networking, storage and automotive.