10G Ethernet Switch IP

Filter

Compare

24

IP

from

13

vendors

(1

-

10)

-

10G Unmanaged Ethernet Switch

- No con figuration required

- Full-crossbar matrix among ports implemented to allow maximum throughput

-

100M/1G/2.5G/5G/10G Managed Ethernet Switch

- Full-duplex 100M/1G/2.5G/5G/10G Ethernet Interfaces

- Configurable from 3 up-to 32 Ethernet ports

-

10G automotive Ethernet switch/TSN IP for advanced integrated architectures

- Updated TSN feature set

- Enhanced diagnostic

- ASIL-B ISO26262

- Configuration tools

-

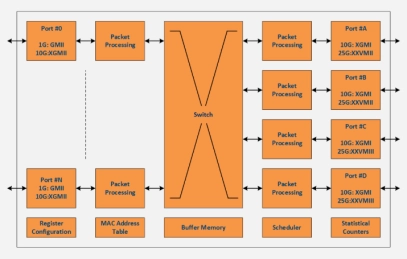

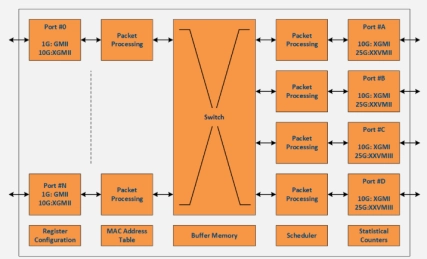

10M/100M/1G/10G/25G Unmanaged Ethernet Switch

- Unmanaged Ethernet Switch IP cores are a family of Ethernet switching IPs that provide a variety of port configurations, including 1G, 1G/10G, 10G, and 10G/25G options.

- The unmanaged Ethernet switch IP cores family is a size-optimized implementation of non-blocking crossbar switches designed to support wire-speed packet processing and forwarding.

-

10M/100M/1G/10G/25G Unmanaged Ethernet Switch

- Unmanaged Ethernet Switch IP cores are a family of Ethernet switching IPs from Comcores that provide a variety of port configurations, including 1G, 1G/10G, 10G, and 10G/25G options.

- The unmanaged Ethernet switch IP cores family is a size-optimized implementation of non-blocking crossbar switches designed to support wire-speed packet processing and forwarding.

-

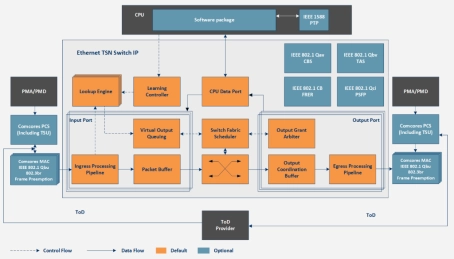

10M/100M/1G/10G/25G Advanced Ethernet TSN Switch IP

- The 10M/100M/1G/10G/25G/100G Ethernet Switching IP is an advanced Ethernet TSN Switch IP with an extensive set of QoS features and statistics.

- The Ethernet TSN Switch IP supports up to 8 queues, classification, VLAN 802.1Q, multicast and broadcast as well as IEEE 1588 transparent clock.

- Each port provides a native interface for Ethernet PHY devices. IEEE 802.1 Protocol Implementation Conformance Statement is available, specifying exact feature-set.

-

1G/10G/25G Switching Ethernet Subsystem

- Supports 1.25G or 10.3125G Ethernet

- Both media access control (MAC) and physical coding sublayer/physical medium attachment (PCS/PMA) functions are included

- Detailed statistics gathering

- Optional support for IEEE 1588 2-step hardware timestamping

-

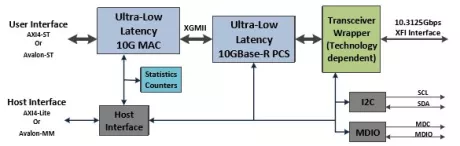

10G Ultra Low Latency Ethernet Solution

- Ultra low latency MAC; Tx = 12.4ns , Rx = 15.5ns; (32-bit user interface mode)

- Ultra low latency 10GBase-R PCS; Tx = 12.4ns, Rx = 12.4ns