MIPI LLI IP

The MIPI LLI controller IP cores are designed to provide MIPI LLI compliant connectivity for a peripheral device. The MIPI Low Latency Interface, MIPI LLI, provides a point-to-point interface between the application processor and modem/baseband processor.

All offers in

MIPI LLI IP

Filter

Compare

3

MIPI LLI IP

from

2

vendors

(1

-

3)

-

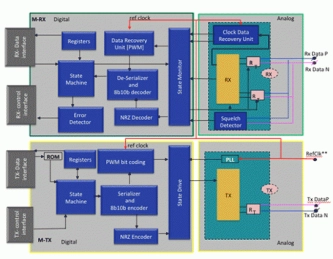

MIPI M-PHY® 4.1 Analog Transceiver

- The M-PHY is of Type 1, which apply to UFS, LLI, and CSI-3 protocols. The Multi-gear M-PHY 4.1 consists of analog transceivers, high-speed PLL, data recovery units as well as state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant with the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

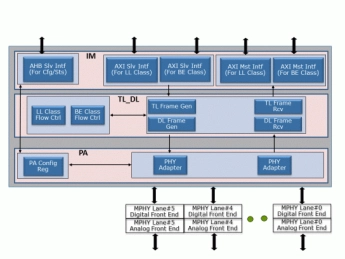

MIPI LLI Controller

- The LLI Controller connects two chips together to create a single “virtual chip”, with both chips sharing the same memory.

- This is achieved by the low latency from the “companion” chip to the memory interface of the host chip.

-

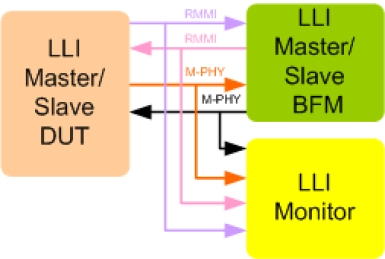

MIPI LLI Verification IP

- Supports MIPI LLI specification 1.0.

- Support MIPI MPHY Type-I specification

- PHY layer supports MPHY serial, MPHY RMMI (10,20,40 bit) Interface

- PHY layer supports multi lanes, Type-I and all power modes for Mphy