Peripheral IP for UMC

Welcome to the ultimate

Peripheral IP

for

UMC

hub! Explore our vast directory of

Peripheral IP

for

UMC

All offers in

Peripheral IP

for

UMC

Filter

Compare

25

Peripheral IP

for

UMC

from

7

vendors

(1

-

10)

-

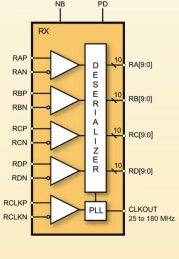

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

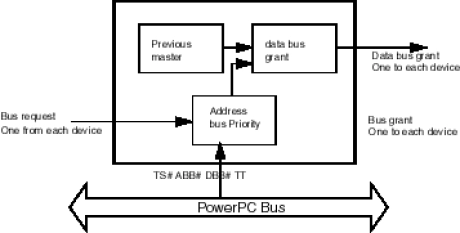

PowerPC Bus Arbiter

- Fully supports PowerPC 60x bus protocol, include PowerPC 603, 604, 740, 750 and 8260.

- Designed for ASIC or PLD implementations in various system environments.

- Fully static design with edge triggered flip-flops.

- Supports up to eight PowerPC bus masters with unlimited slave device support.

-

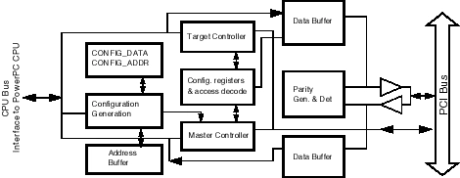

PowerPC to PCI Bridge

- Fully supports PCI specification 2.1 and 2.2 protocol.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Supports all PowerPC CPU with 603 bus interface and MPC860 interface.

-

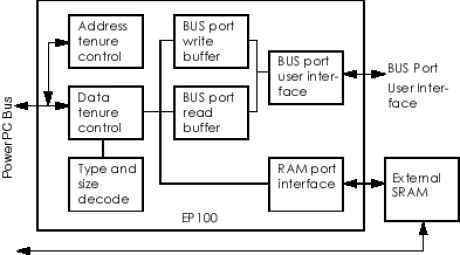

PowerPC Bus Slave

- Fully supports PowerPC 60x bus protocol including PowerPC 603, 604, 740, 750 and MPC8260.

- Designed for ASIC or PLD implementations in various system environ-ments.

- Fully static design with edge triggered flip-flops.

- Direct support for standard asynchronous SRAM and synchronous BURST SRAM.

-

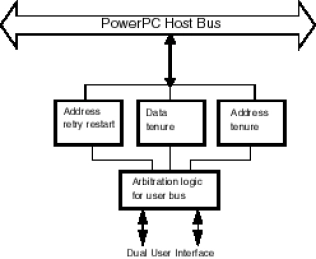

PowerPC Bus Master

- Fully supports PowerPC 60x bus protocol, include PowerPC 603, 604, 740, 750 and 8260.

- Designed for ASIC or PLD implementations in various system environments.

- Fully static design with edge triggered flip-flops.

- Automatic bus arbitration for address bus and data bus based on internal bus request.

-

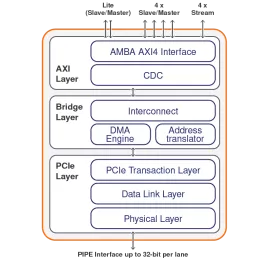

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

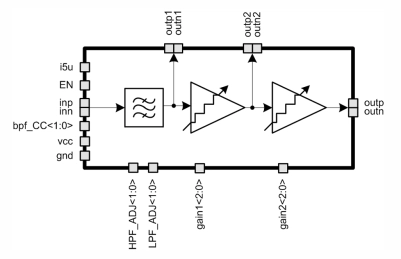

15 to 2780 kHz amplifier with band-pass filter

- UMC CMOS 0.18 um

- Low consuming

- Wide gain adjustment range

- Differential input and output

-

Configurable Watchdog Timer

- AMBA APB4-Lite bus

- Configurable timeout interval

- Standard and windowed mode

- Register write protection

-

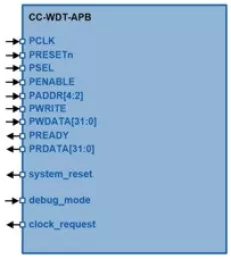

Configurable Watchdog Timer

- AMBA APB3 bus

- Configurable timeout interval

- Standard and windowed mode

- Register write protection

-

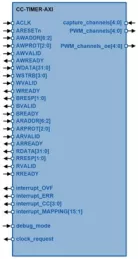

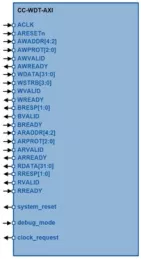

Configurable Timer Counter

- AMBA AXI4-Lite bus

- Programmable multi-function timer

- Double buffered configuration registers

- Configurable single/dual slope PWM outputs