PLL IP for UMC

Welcome to the ultimate

PLL IP

for

UMC

hub! Explore our vast directory of

PLL IP

for

UMC

All offers in

PLL IP

for

UMC

Filter

Compare

477

PLL IP

for

UMC

from

12

vendors

(1

-

10)

-

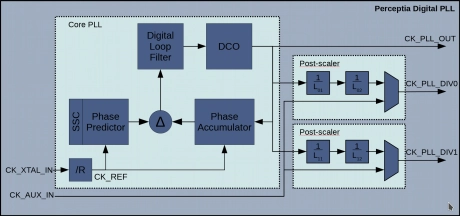

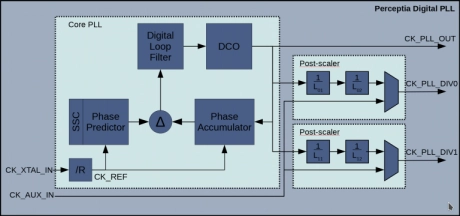

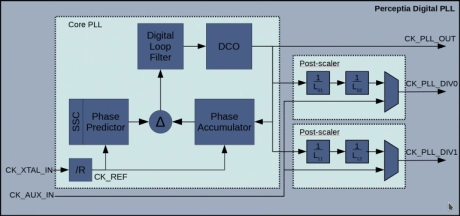

All Digital Fractional-N PLL for Performance Computing in UMC 40LP

- Fractional multiplication with frequency up to 4GHz

- Low jitter (< 10ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 5mW)

-

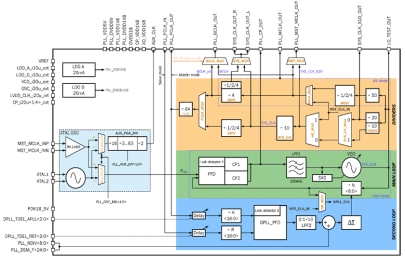

2.26GHz/2.46GHz Fractional-N LC Phase-Locked Loop with oscillator

- 180XFAB_PLL_01 uses 2.25792GHz/2.4576GHz Phase locked loop frequency synthesizer for clock generation.

- It consists of the following main sub-blocks: reference oscillator; main PLL loop: Fractional-N PLL and VCO blocks; secondary digital PLL loop: synchronization subsystem; dividers block: clock generation/delivery subsystem; voltage stabilizers.

- High frequency synthesis is needed for both phase noise performance and ultra-fine frequency tuning step.

-

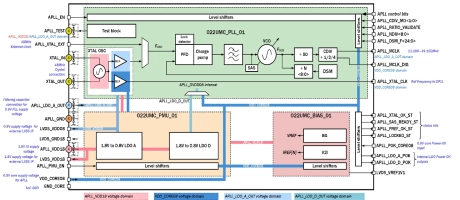

10MHz to 50MHz fractional-N PLL synthesizer

- UMC 22nm ULP technology

- 1.8V IO power supply

- Double 0.8/1.0V Core power supply

- Embedded low noise bias

-

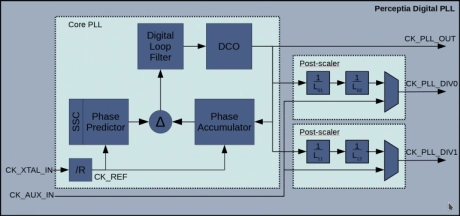

All Digital Fractional-N RF Frequency Synthesizer PLL in UMC 40LP

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (< 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 15mW)

-

General Purpose All Digital Fractional-N PLL in UMC 40LP

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

General Purpose All Digital Fractional-N PLL in TSMC N6/N7

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

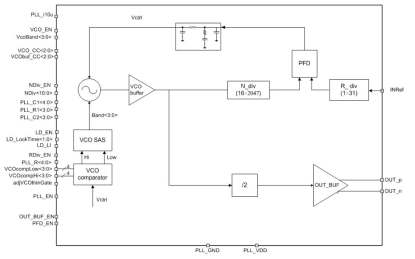

Phase-locked loop frequency synthesizer

- CMOS UMC 65 nm

- Integer-N frequency synthesizer with good phase noise performance

- Guaranteed frequency range 550…750 MHz

- Wide continuous loop frequency divider ratio range (16..2047 with step 1) allow to cover frequency range using different reference frequency

-

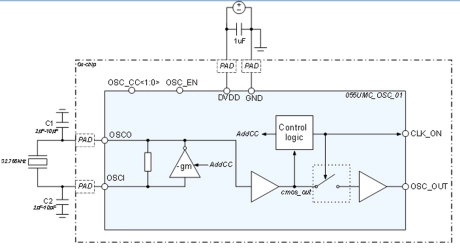

Ultra low power 32.768 kHz crystal oscillator

- UMC 55nm eFlash CMOS technology

- Input Voltage 1.2V

- Fixed 32.768kHz output frequency

-

Integer-N PLL, 32M ~ 256MHz on UMC 55nm

- This present IP is a Phase Locked Loop (PLL) circuit

- It’s analog PLL suitable for various frequency node generations

- The VCO can run from 32MHz to 256MHz

- It contains input clock divider (DIVM), a feedback clock divider (DIVN) and level shifter block to switch signals between VDD12 and VDD33

-

24-Bit Accuracy Fractional PLL; Support 8K~192K*256 Clock Output - UMC 55nm

- 24-Bit Accuracy Fractional PLL; Support 8K~192K*256 Clock Output