Interface Security IP for TSMC

Welcome to the ultimate

Interface Security IP

for

TSMC

hub! Explore our vast directory of

Interface Security IP

for

TSMC

All offers in

Interface Security IP

for

TSMC

Filter

Compare

12

Interface Security IP

for

TSMC

from

2

vendors

(1

-

10)

-

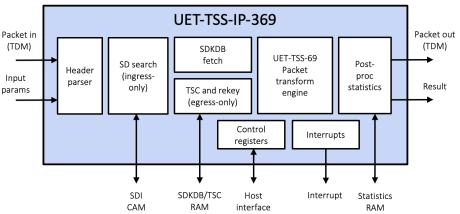

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

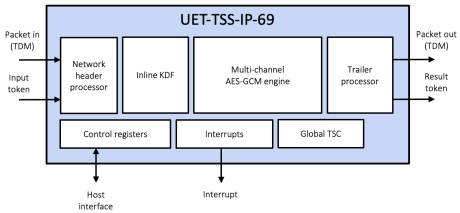

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

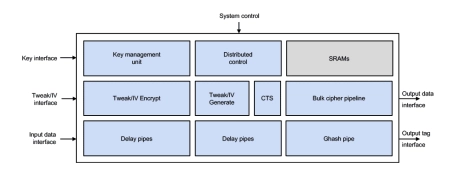

Fast Inline Cipher Engine, AES-XTS/GCM, SM4-XTS/GCM, DPA

- One input word per clock without any backpressure

- Design can switch stream, algorithm, mode, key and/or direction every clock cycle

- GCM: throughput is solely determined by the data width, data alignment and clock frequency

- XTS: block processing rate may be limited by the number of configured tweak encryption & CTS cores; a configuration allowing 1 block/clock is available

-

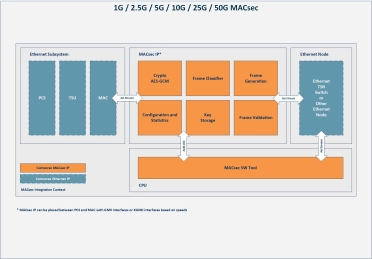

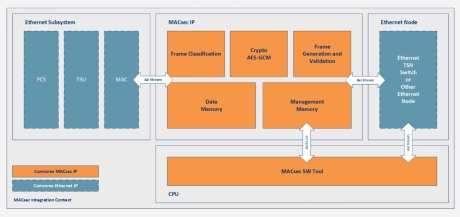

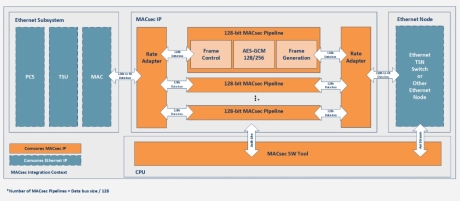

1G/2.5G/5G/10G/25G/50G MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially high-speed Ethernet used in automotive, industrial, cloud, data center, and wireless infrastructure.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and supports VLAN-in-Clear.

-

10M MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially very low-speed Ethernet used in automotive, industrial, and consumer applications.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and is optimized for the smallest area size.

-

100G / 200G / 400G / 800G / 1.6T MACsec

- The MACsec IP provides Ethernet Layer 2 Security for port authentication, data confidentiality and data integrity as standardized in IEEE 802.1AE.

- It protects components in Ethernet networks especially very high-speed Ethernet used in cloud, data center, and backhaul networks.

- The MACsec IP is a fully compliant solution that provides line-rate encryption and supports VLAN-in-Clear.

-

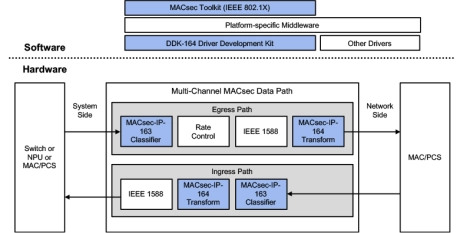

800G Multi-Channel MACsec Engine with TDM Interface

- Complete and fully compliant MACsec Packet Engine with classifier and transformation engines for rates of 100 to 800 Gbps, up to 64 channels, ready for FlexE

- All IEEE MACsec standards supported (including IEEE802.1AE-2018). Optional inclusion of Cisco extensions, IPsec ESP tunnel and transport mode with AES-GCM cipher

- Supplied with the Driver Development Kit to accelerate time to market. Rambus offers MACsec Toolkit for IEEE 802.1X key management

-

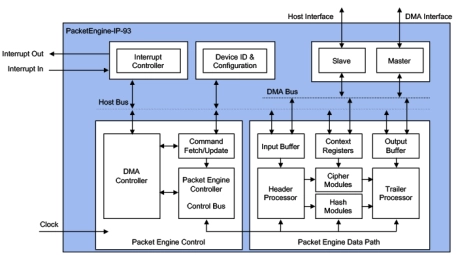

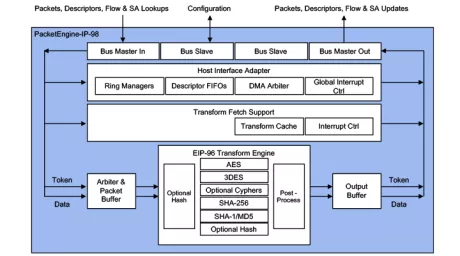

Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP and MACsec Packet Engine with virtualization, caches classifier and Look-Aside interface for multi-core application processors

- 5-10 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP, DPDK, Linux Crypto

-

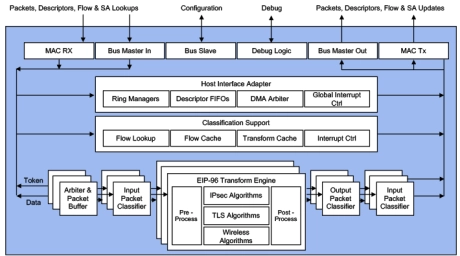

Multi-Protocol Engine with Classifier, Inline and Look-Aside, 10-100 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP, MACsec packet engine with classifier and in-line interface for multi-core server processors

- 10-100 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, streaming and AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP.

-

Multi-Protocol Engine, Look-Aside, 1 Gbps

- Protocol-aware IPsec/TLS packet engine with Look-Aside interface for IoT.

- Up to 1 Gbps, lowest gate count in the industry, just 100K gates (ex AMBA interface).

- Supported by Driver Development Kit, QuickSec IPsec toolkit, Secure Boot Toolkit.