Video Codec IP for TSMC

Welcome to the ultimate

Video Codec IP

for

TSMC

hub! Explore our vast directory of

Video Codec IP

for

TSMC

All offers in

Video Codec IP

for

TSMC

Filter

Compare

22

Video Codec IP

for

TSMC

from

7

vendors

(1

-

10)

-

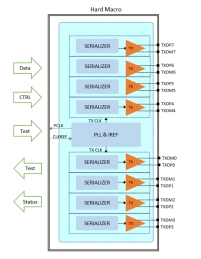

SLVS-EC TX PHY - 10GBPS 8-Lane - TSMC 12FFC

- SLVS-EC ver.3.0 compliant

- Data Rate: Up to 10Gbps / lane

- Number of data lane: 8

- Support input clock: 24MHz, 54MHz, 37.125MHz, 72MHz, 74.25MHz

-

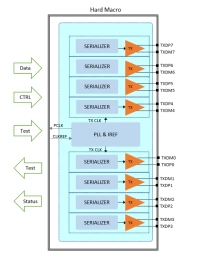

Camera Receiver - 10.0Gbps 8-Lane - TSMC 12FFC

- The CL12812M8RIP10000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processor) and DSP.

- The CL12812M8RIP10000 is designed to support data rate in excess of maximum 10Gbps utilizing SLVS-EC ver.3.0 interface specification.

-

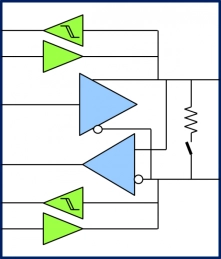

LVDS interfaces

- Wide operating range

- High data rates

- Very flexible programmability

- Excellent signal integrity

- TIA/EIA644A LVDS and sub-LVDS compatibility

- Receiver also compatible with LVPECL

-

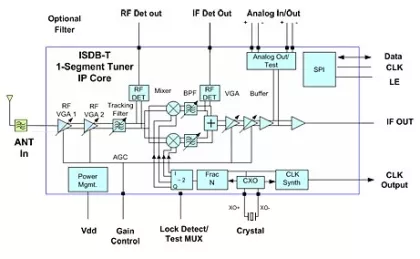

ISDB-T1, Segment Tuner (470-860MHz UHF)

- High Performance

- Configurable 3/4 wire controller

- Self calibrating and programmable filter corner frequencies

- 8 Bit electronically tunable tracking filter

-

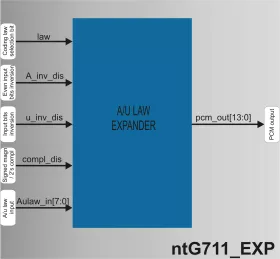

ITU G.711 expander

- Expands 8 bit a-law or u-law logarithmic PCM to 13/14 bit linear PCM.

- Compliant to the ITU G.711 standard.

- Purely combinational logic RTL implementation.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

-

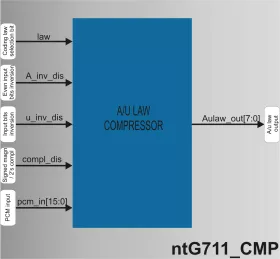

ITU G.711 compressor

- Compresses 16-bit linear PCM to 8 bit a-law or u-law logarithmic PCM.

- Compliant to the ITU G.711 standard.

- Purely combinational logic RTL implementation.

- Silicon proven in ASIC and FPGA technologies for a variety of applications.

-

Camera Combo Receiver - 2.4Gbps 8-Lane - TSMC 28nm HPC

- The CL12832M8R2JM3KIP2400 is designed to support data rate in excess of maximum 2.4Gbps utilizing SLVS-EC / sub-LVDS / CMOS 1.8V interface specification.

- The CL12832M8R2JM3KIP2400 can change Interface type to same PAD for changing mode.

-

Configurable SPDIF-AES3 Transmitter

- The SPDIF-Tx-Pro (CWda15) is a digital audio transmitter IP core supporting the SPDIF IEC60958 and AES3 standards for PCM audio and the IEC61937 and SMPTE 337M standards for non-PCM (compressed) audio.

- The core is very configurable allowing many features of the standards to be optionally supported by hardware or software.

-

Configurable SPDIF-AES3 Receiver

- The SPDIF-Rx-Pro (CWda14) is a digital audio receiver IP core supporting the SPDIF and AES3 and IEC60958 standards and also adds hardware support for the IEC61937 and SMPTE 337M standards for non-PCM (compressed) audio.

- This purely digital clock and data recovery method dispenses the classical analog PLL at the input reducing the receiver cost.

-

Single-core video encoder - AV1, HEVC, AVC

- YUV420/YUV422/YUV444

- 8/10-bit depth

- I/P/B-frame

- Frame buffer compression

- Multi-instances