Memory & Libraries IP for TSMC

Welcome to the ultimate

Memory & Libraries IP

for

TSMC

hub! Explore our vast directory of

Memory & Libraries IP

for

TSMC

All offers in

Memory & Libraries IP

for

TSMC

Filter

Compare

26

Memory & Libraries IP

for

TSMC

from

6

vendors

(1

-

10)

Filter:

- 6nm

-

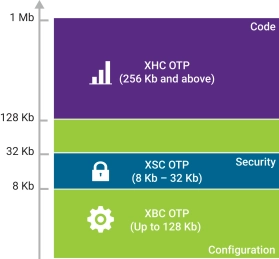

NVM OTP XBC TSMC N6 1.8V

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

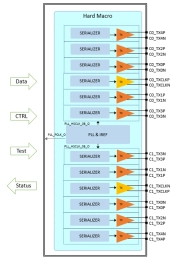

LVDS / sub-LVDS / DPHY TX - TSMC 6FFC

- The LVDS/Sub-LVDS/DPHY Combo TX converts parallel RGB data and 7/8/10 bits of CMOS parallel data into serial data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated high-speed link.

- The polarity of differential signals for each data lane can be controlled.

-

Standard Cell

- Dolphin offers an extensive array of Standard Cell libraries that have been methodically tested and verified in silicon for each process technology supported.

- More than 3500 fully customizable cells are available, and each has been optimized for speed, routability, power and density, in order to maximize performance and wafer yield while lowering overall SoC cost.

-

I/O Library

- Dolphin Technology offers an extensive array of Interface IP, all of whichhasbeen optimized for ultra high performance across all processes supported.

- Our I/O portfolio includes: Standard I/O (General Purpose I/O or GPIO), Specialty I/O (bus-specific I/O), NAND Flash I/O and DDRx & LPDDRx I/O.

-

Memory Compilers

- Dolphin provides a wide range of Memory Compilers and Specialty Memory (ROM, Multi Port RF, CAM, etc.) optimized to meet even the most demanding requirements for high performance, high density and low power.

-

TSMC N6 1.8V/3.3V Fail-Safe Fail-Tolerant SMBus

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.2V/1.8V/2.5V/3.3V Fail-safe GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.2V/1.8V/2.5V/3.3V GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.8V/2.5V/3.3V GPIO

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N6 1.8V/2.5V/3.3V I3C IO

- Synopsys I3C IO library supports a simplified system of connecting and managing multiple sensors in a device

- Multiple sensor secondary devices can be controlled by one I3C primary device at a time

- It offers backward compatibility with I2C legacy devices, is designed for high IO voltage domains and supports low-core voltage domains

- The I3C incorporates the Schmitt-Trigger function, supports I2C Legacy Fast Mode and FM+ Mode, and includes HBM and CDM ESD protection