MIPI Controller IP for TSMC

Welcome to the ultimate

MIPI Controller IP

for

TSMC

hub! Explore our vast directory of

MIPI Controller IP

for

TSMC

All offers in

MIPI Controller IP

for

TSMC

Filter

Compare

7

MIPI Controller IP

for

TSMC

from

3

vendors

(1

-

7)

-

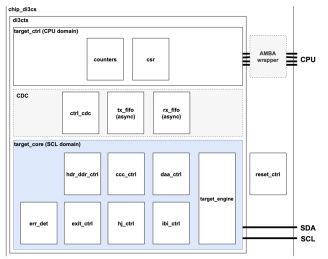

MIPI I3C Target Device

- MIPI I3C Basic Specification v1.2 compiliance

- Native 32-bit CPU Interface

- Optional CPU interface wrappers (APB, AHB, AXI)

- Legacy I2C communication with 7-bit Static Address

- I3C Single Data Rate (SDR) mode

-

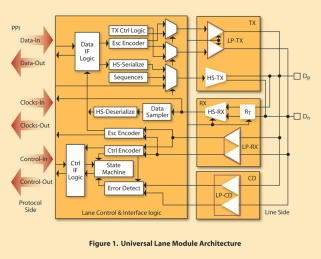

MIPI D-PHY IP

- The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module.

- This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

-

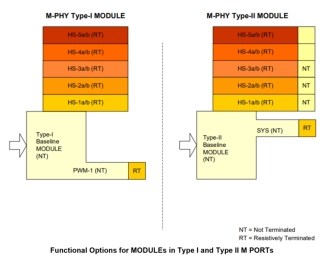

MIPI M-PHY IP

- The MIPI M-PHY is a high-frequency low-power, Physical Layer IP that supports the MIPI® Alliance Standard for M-PHY.

- The IP can be used as a physical layer for many applications, connecting flash memory-based storage, cameras and RF subsystems, and for providing chip-to-chip inter-processor communications (IPC).

-

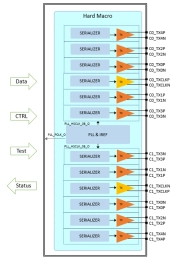

LVDS / sub-LVDS / DPHY TX - TSMC 6FFC

- The LVDS/Sub-LVDS/DPHY Combo TX converts parallel RGB data and 7/8/10 bits of CMOS parallel data into serial data streams.

- A phase-locked clock is transmitted in parallel with the data streams over a dedicated high-speed link.

- The polarity of differential signals for each data lane can be controlled.

-

MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- Conforms to MIPI I3C v1.1 specifications

- MIPI Manufacturer ID: 0x03B3

- Dynamic Addressing while supporting Static Addressing for Legacy I2C Devices

- Legacy I2C messaging

-

Camera Combo Receiver - 5.0Gbps 8-Lane - TSMC 12FFC, 7FF

- The CL12842M8RM3AM5AIP5000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processor) and DSP.

- The CL12842M8RM3AM5AIP5000 is designed to support data rate in excess of maximum 5Gbps utilizing SLVS-EC ver.2.0 / MIPI D-PHY ver.1.2 / HiSPi / sub-LVDS / CMOS 1.8V interface specification.

-

Camera Combo Receiver - 5.0Gbps 8-Lane

- The CL12822M4R2JM2LIP5000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processer) and DSP.

- The CL12822M4R2JM2LIP5000 is designed to support data rate in excess of maximum 5.0Gbps utilizing SLVS-EC ver.2.0 / MIPI D-PHY v2-1 interface specification. The CL12822M4R2JM2LIP5000 can change Interface type to same PAD for changing mode.