Other for TSMC

Welcome to the ultimate

Other

for

TSMC

hub! Explore our vast directory of

Other

for

TSMC

All offers in

Other

for

TSMC

Filter

Compare

4

Other

for

TSMC

from

2

vendors

(1

-

4)

Filter:

- 28nm

-

32Gbps, 31 order, Pseudo Random Bit Sequence Generator / Checker

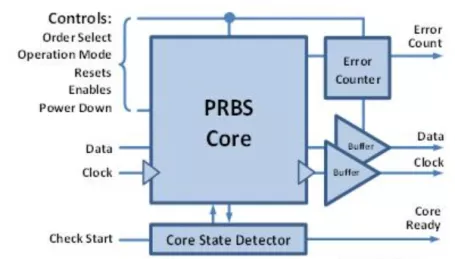

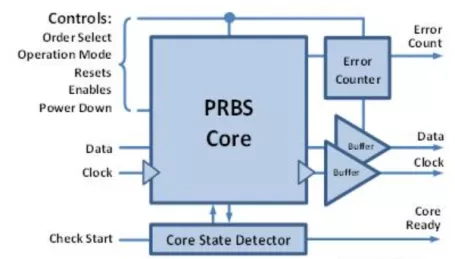

- This unit generates and checks Pseudo Random Bit Sequence (PRBS) of 31 order, up to 32Gbps. Error count is accurate: no double counts or omissions regardless of error sequence or frequency of occurrence.

- Can be used as Generator, Checker or both. No inductors are used minimizing area and EM interference. Simple control interface, with low frequency asynchronous signals only.

-

32Gbps, 7/15/31 order, Pseudo Random Bit Sequence Generator/Checker

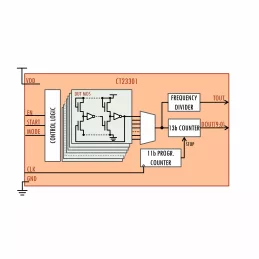

- PRBS order: 7, 15 or 31 based on formulas: X1=X6^X7; X1=X14^X15; X1=X28^X31

- Full bit rate at input and output up to 32Gbps

- Generator, Checker and Counter functions

- Accurate error count: no omissions or double counts

- Full rate CMOS differential input data, centered with half-rate CMOS differential clock

- Full rate CMOS differential output data, aligned with half-rate CMOS differential clock

-

-

32Gbps Pseudo Random Bit Sequence Generator/Checker

- PRBS order: 7 or 15 based on formulas: X1=X6^X7; X1=X14^X15

- Full bit rate at input and output up to 32Gbps

- Generator, Checker and Counter functions

- Accurate error count: no omissions or double counts

- Full rate CMOS differential input data, centered with half-rate CMOS differential clock

- Full rate CMOS differential output data, aligned with half-rate CMOS differential clock

- Asynchronous low frequency CMOS control interface

- Supply voltage: 0.9V