Analog IP for TSMC

Welcome to the ultimate

Analog IP

for

TSMC

hub! Explore our vast directory of

Analog IP

for

TSMC

All offers in

Analog IP

for

TSMC

Filter

Compare

245

Analog IP

for

TSMC

from

22

vendors

(1

-

10)

Filter:

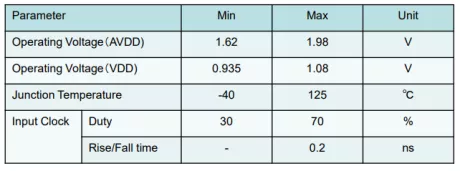

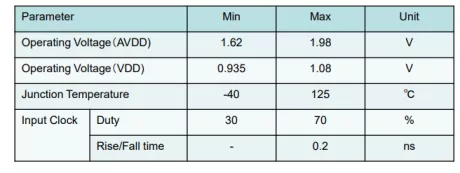

- 28nm

-

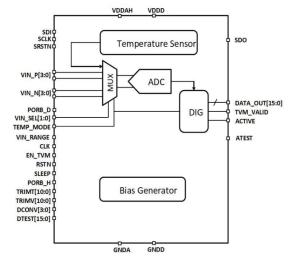

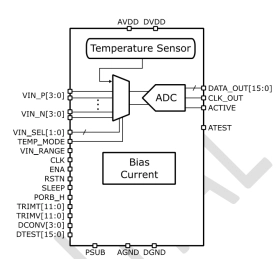

Ultra-Low-Power Temperature/Voltage Monitor

- ± 4C temperature accuracy without trim

- ± 1C temperature accuracy after single room temperature trim

- 0.011C temperature resolution

- Voltage monitor supports both single-ended and differential inputs, with 4:1 input mux

-

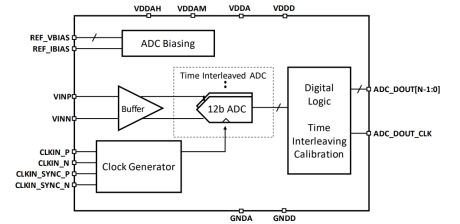

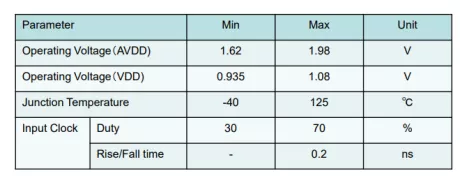

Ultra high-performance low-power ADC

- TSMC 28nm

- Ultra high-performance low-power ADC

- 12-bit ADC resolution

- Sampling rate up to 5GSPS

-

1.7GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 850MHz - 1700 MHz

- Output frequency range : 850MHz -1700 MHz

- Input frequency range : 9.6MHz - 216MHz

-

5GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 2500MHz - 5000 MHz

- Output frequency range : 1250MHz - 2500 MHz

- Input frequency range : 12MHz - 320 MHz

-

1.8GHz SSCG PLL on TSMC 28nm HPC+

- Including Loop-filter

- VCO operating range : 900MHz - 1800 MHz

- Output frequency range : 900MHz-1800 MHz

- Input frequency range : 12MHz - 192MHz

-

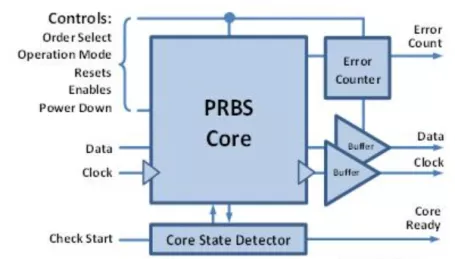

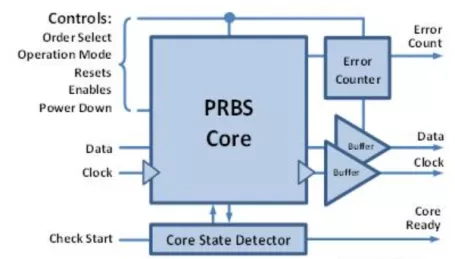

32Gbps, 31 order, Pseudo Random Bit Sequence Generator / Checker

- This unit generates and checks Pseudo Random Bit Sequence (PRBS) of 31 order, up to 32Gbps. Error count is accurate: no double counts or omissions regardless of error sequence or frequency of occurrence.

- Can be used as Generator, Checker or both. No inductors are used minimizing area and EM interference. Simple control interface, with low frequency asynchronous signals only.

-

32Gbps, 7/15/31 order, Pseudo Random Bit Sequence Generator/Checker

- PRBS order: 7, 15 or 31 based on formulas: X1=X6^X7; X1=X14^X15; X1=X28^X31

- Full bit rate at input and output up to 32Gbps

- Generator, Checker and Counter functions

- Accurate error count: no omissions or double counts

- Full rate CMOS differential input data, centered with half-rate CMOS differential clock

- Full rate CMOS differential output data, aligned with half-rate CMOS differential clock

-

Ultra-Low-Power Temperature/Voltage Monitor in 28nm CMOS

- The ODT-TVM-ULP-001C-28 is an ultra-low power temperature and voltage monitor designed in a 28nm standard CMOS process.

- This IP operates over the entire temperature range of -40°C to 150°C.

- The temperature monitor achieves ±4C temperature accuracy without trim and ±1C temperature accuracy after a single room temperature trim.

-

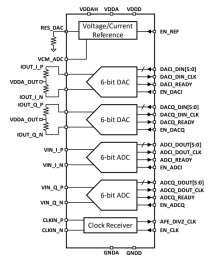

6-bit, 1 GSPS High Performance AFE in 28nm CMOS

- The ODT-AFE-6B1G-28HPCPT is a highperformance I/Q ADC and I/Q DAC designed in a 28nm CMOS process.

- The 6-bit, 1.056GSPS I/Q ADC supports input signals up to 400 MHz and features a differential full-scale range of 0.6Vpp and excellent static and dynamic performance.

- The ADC architecture is optimized to maximize performance while minimizing power and area consumption.

-

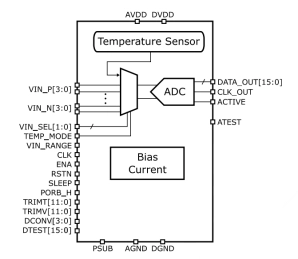

Ultra-Low-Power Temperature/Voltage Monitor in GF 22FDX

- The ODT-TVM-ULP-001C-GF22FDX is an ultra-low power temperature and voltage monitor designed in a 22nm process.

- This IP operates over the entire temperature range of -40°C to 150°C.

- The temperature monitor (TM) achieves ±4°C temperature accuracy without trim and ±1°C temperature accuracy after a single room temperature trim.