The MXL-DPHY-CSI-2-RX+ is a high frequency low-power, low-cost, source-synchronous, Physical Layer compliant with the MIPI Alliance Standard for D-PHY.

The IP is configured as a MIPI slave optimized for camera interface applications (CSI2).

The RX+ is a Mixel proprietary D-PHY configuration that enables Mixel's customers to achieve full-speed testability while minimizing power and area.

MIPI D-PHY CSI-2 RX+ (Receiver) IP in TSMC 28HPM

Overview

Key Features

- Consists of 1 Clock lane and 2 Data lanes

- Complies with MIPI Standard 1.1 for D-PHY

- Supports both high speed and lowpower modes

- 80 Mbps to 1.5Gbps data rate in high speed mode

- 20 Mbps data rate in low-power mode

- High Speed Deserializers included

- Low power dissipation

- Proprietary features supporting full-speed testability with reduced power and area

Benefits

- Comprehensive embedded DFT features for allowing cost-effective high-volume manufacturing tests

- Supports full-speed loopback testability with minimal area overhead for high-volume manufacturing tests

- Embedded PLL with compact footprint used for generating high-speed clock during test modes and eliminates the need for an external PLL.

- One transmitter is used to test multiple receivers to minimize area overhead

- Two different loopback modes allow isolation of faults and defects

- Analog test bus (ATB) for sensing internal analog voltages and currents

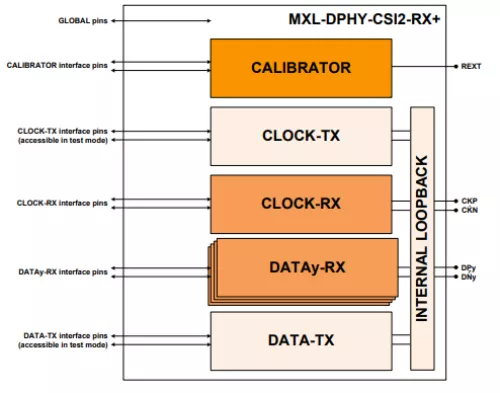

Block Diagram

Applications

- Mobile

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

TSMC 28nm HPM

Maturity

Silicon Proven

Availability

Now

TSMC

Silicon Proven:

28nm

HPM