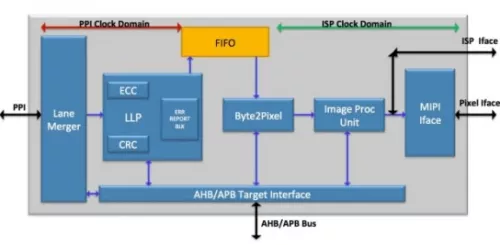

The CSI-2 Receiver IP Core functions as a MIPI Camera Serial Interface (CSI-2 Combo) Receiver, which interfaces between a peripheral device (Camera module) and a host processor (baseband, application engine).

The CSI-2 Combo Receiver IP communicates over a D-PHY (or) C-PHY serial link to image processing block, part of the application engine. The CSI-2 combo IP is MIPI compliance and provides a standard, scalable, low-power, high-speed interface that supports a wide range of higher image resolutions.

Compliant with the following MIPI specifications

- mipi_CSI-2_specification_v1-3

- mipi_D-PHY_specification_v1-2

- mipi_C-PHY_specification_v1-1