RISC-V to the Core: New Horizons

The increasing popularity of the RISC-V ISA within the semiconductor industry is a boon for innovation. It provides designers with unprecedented flexibility and will slowly but steadily challenge and transform the current landscape of embedded systems. In the past, Renesas has embraced RISC-V technology introducing 32-bit ASSP devices for voice-control and motor-control built on CPU cores developed by Andes Technology Corp.

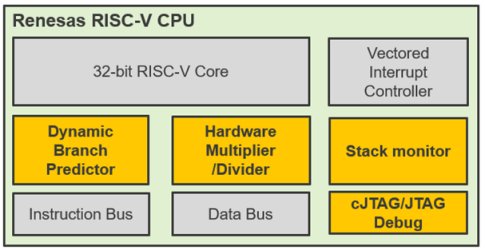

The exciting next step is the availability of the first, in-house engineered, CPU core. A high-level block diagram of the CPU is shown below:

But what‘s so special about it? First, this CPU is suitable for many different application contexts. It can be used as main CPU or to manage an on-chip subsystem or even to be embedded in a specialized ASSP device. Clearly it is very flexible. Second, the implementation is very efficient in terms of silicon area, which helps reduce operating current and leakage current during standby time, besides the obvious effect of smaller cost impact. Third, despite targeting small embedded systems, it provides a surprisingly high level of computational throughput to fulfill the increasingly demanding performance requirement of even deeply embedded applications.

To read the full article, click here

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related Blogs

- Imagination Technologies' Upgraded GPUs, New Neural Network Core Provide Deep Learning Processing Options

- New AXI Scatter-Gather DMA Core Transfers Streaming Data to/from System Memory

- Developing a customized RISC-V core for MEMS sensors

- Ambient IoT: 5 Ways Packetcraft's Software is Optimized to Enable the New Class of Connectivity

Latest Blogs

- Synopsys Advances Die‑to‑Die Connectivity with 64G UCIe IP Tape‑Out

- The 5 Biggest Challenges in Modern SoC Design (And How to Solve Them)

- Can Your NPU Run DOOM? Chimera Can.

- Importance Of Hardware Security Verification In Pre-Silicon Design

- Arteris × XuanTie: The “Data Highway” for High-Performance RISC-V SoCs