PCIe 6.x and 112 Gbps Ethernet: Synopsys and TeraSignal Achieve Optical Interconnect Breakthroughs

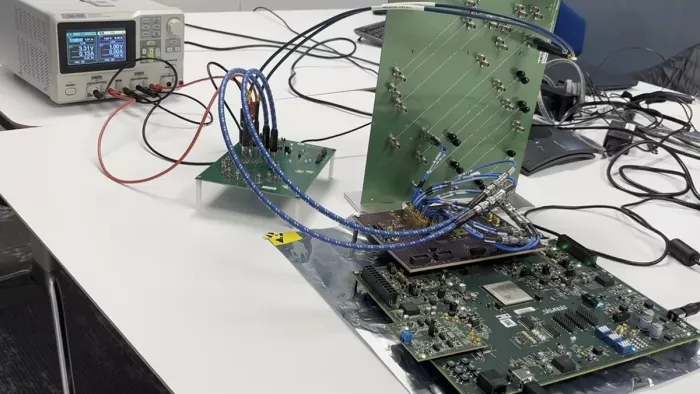

Synopsys and TeraSignal have reached two milestones in optical networking, demonstrating seamless interoperability for PCIe 6.x and 112 Gbps Ethernet over linear optics.

These industry-first achievements highlight the potential of linear optics to transform data transmission in hyperscale data centers and high-performance computing (HPC) environments.

Synopsys and TeraSignal showcase industry-first interoperability for 112 Gbps Ethernet over linear optics.

Linear optics: Faster data transmission with less power consumption

Copper cables — the traditional backbone of data transmission — are struggling to meet the speed, power efficiency, and performance demands of modern computing environments and workloads.

Linear optics offer a compelling alternative, providing faster data transmission over long distances with less power consumption and minimal signal loss.

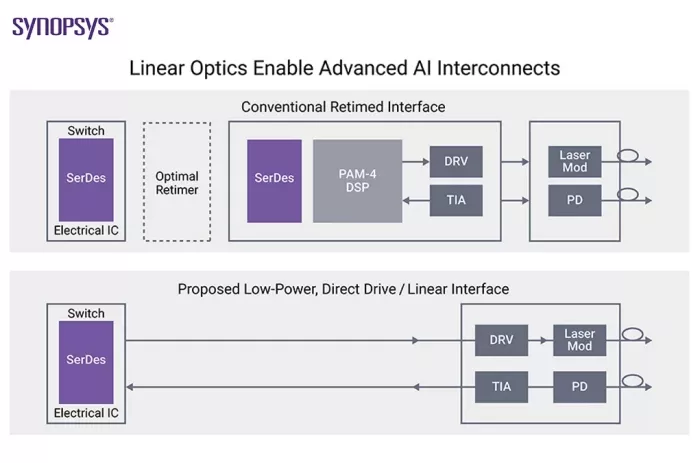

- No retimers or DSPs: Linear optics eliminate the need for power-hungry components like retimers and digital signal processors (DSPs).

- Efficiency gains: Linear optics can reduce power consumption by up to 50%, lower latency, and generate less heat compared to legacy cabling infrastructure.

- Simplified design: Linear optics simplify the data path, making it ideal for hyperscale and HPC environments and demanding applications like artificial intelligence (AI) and machine learning (ML).

By reducing energy consumption, minimizing latency, and mitigating heat generation, linear optics provide an ideal solution for performance-intensive and power-sensitive applications. And because they can be deployed alongside traditional cable interconnects, linear optics give data center operators more flexibility to fine-tune their infrastructure for each workload.

Before linear optical technologies can be broadly adopted, however, interoperability with industry standard interfaces — like PCIe 6.x and 112 Gbps Ethernet — must be assured.

Industry-first interoperability between linear optical modules and PCIe/Ethernet interfaces

In collaboration with TeraSignal — a leader in high-speed data transmission — we demonstrated how linear optical modules and advanced IP interfaces can help transform hyperscale data centers and HPC environments.

Showcased at DesignCon 2025 and OFC 2025, these industry-first demonstrations paired:

- Synopsys 112G Ethernet PHY IP with TeraSignal TSLink Intelligent Driver, a protocol-agnostic linear optical interconnect.

- Highlights: Strong signal integrity and real-time signal optimization resulted in an extremely low error rate (E-11).

- Takeaway: The ability to manage high data speeds with outstanding reliability represents a significant step forward in optical connectivity.

- Synopsys PCIe 6.x IP with TeraSignal TS5602 Intelligent Re-Driver, a retimer-less solution for PCIe 6.0 over optics.

- Highlights: Real-time monitoring of digital eye patterns, adaptive link training, and low bit error rates.

- Takeaway: This level of performance and reliability will be necessary to connect and scale AI accelerators, GPUs, and CPUs using PCIe over optics.

Meeting the performance and power demands of AI/ML workloads

Larger datasets and expanding compute clusters have placed networking hardware at the forefront of AI/ML performance and cost efficiency. Interconnecting tens, hundreds, or even thousands of accelerators has become a critical challenge.

The bandwidth, latency, and power efficiency of optical interconnects play a pivotal role in addressing this challenge — helping ensure accelerators, processors, and memory units operate seamlessly and efficiently within hyperscale and HPC environments.

Linear pluggable modules and other advanced optical technologies provide a clear path forward for network optimization and scaling. But interoperability must be seamless and reliable.

Our work with TeraSignal not only demonstrates interoperability — it also advances optical interconnect technology, increases the utility of PCIe and Ethernet interfaces, and reduces the cost and risk of linear optical development and deployment.

White paper: Why HPC Chip Designers are Looking into Linear Pluggable Optics

Webinar: Getting Ready for PCIe and Ethernet Over Linear Pluggable Optics

Related Semiconductor IP

- 112G PHY G2, TSMC N5 x4, North/South (vertical) poly orientation

- PCIe 6.0 (Gen6) Premium Controller

- AXI Bridge with DMA for PCIe IP Core

- PCIe Gen 7 Verification IP

- PCIe Gen 6 Phy

Related Blogs

- The Future of PCIe Is Optical: Synopsys and OpenLight Present First PCIe 7.0 Data-Rate-Over-Optics Demo

- PCIe 6.x: Synopsys IP Selected as First Gold System for Compliance Testing

- Ultra Ethernet Consortium Set to Enable Scaling of Networking Interconnects for AI and HPC

- 50 Gbps Ethernet is on the Way

Latest Blogs

- Universal Browser Support for JPEG XL: Is Your Hardware Ready for the New Standard?

- The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

- Reimagining Chip Design - From Spec to Signoff with Cadence AI Super Agents

- The Architectural Evolution of 16GHz PLLs for Next-Gen AI and SerDes SoCs

- Considerations When Architecting Your Next SoC: NoCs with Arteris