Cadence在2024 PCI-SIG 开发者大会上展示完整的PCIe 7.0解决方案

十多年来,Cadence对PCIe技术的坚定承诺和支持,在业界有目共睹。我们深知强大PCIe生态系统的重要性,并感谢PCI-SIG提供的平台。在PCI-SIG开发者大会迎来32周年之际,Cadence宣布面向HPC/AI市场推出完整的PCIe 7.0 IP解决方案。

PCIe标准为何如此重要?

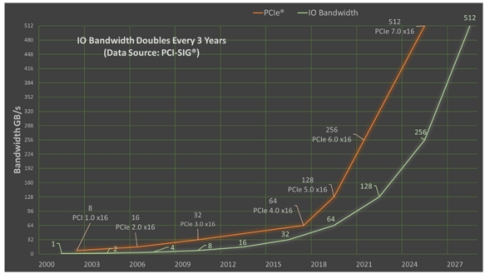

从GPIO等最简单的构建块到最先进的高速接口,IP子系统是整个芯片制造生态系统的命脉。而推动IP发展的一个关键因素便是工业界和学术界在接口标准和协议制定上的合作。PCI-SIG引领了一些关键定义和合规规范的制定,并确保了接口IP的互操作性。

HPC/AI市场不断要求高吞吐量、低延迟和低功耗,这推动着技术的进步,促使PCIe技术持续发展,可服务于未来几代。作为PCI-SIG的成员,Cadence能够尽早获知规范的变化和最新合规标准等重要信息。PCIe 7.0及更高规范将助推市场不断扩展,而我们期待帮助我们的客户使用Cadence IP解决方案构建一流的尖端SoC。

图1:PCIe数据传输速率变化(来源:PCI-SIG)

今年的开发者大会有何新看点?

在2024 开发者大会上,PICe 7.0标准成为焦点,Cadence今年展示了面向 PCI 7.0的一整套IP子系统解决方案。

Cadence有何与众不同之处?

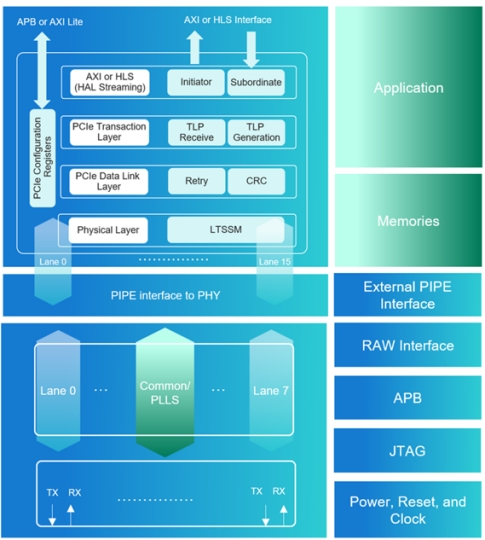

Cadence始终坚持为测试芯片构建一个完整的子系统,包括8通道PHY和一个完整的8通道控制器。在测试芯片中添加一个控制器,可以显著提高特性分析和压力测试的效率和粒度,同时使我们能够展示与真实系统的互操作性。此外,我们还可以将整个协议栈作为一个8通道的解决方案进行测试,其中涵盖客户实际使用的诸多应用。这种方法能够帮助客户大大降低SoC设计相关风险。

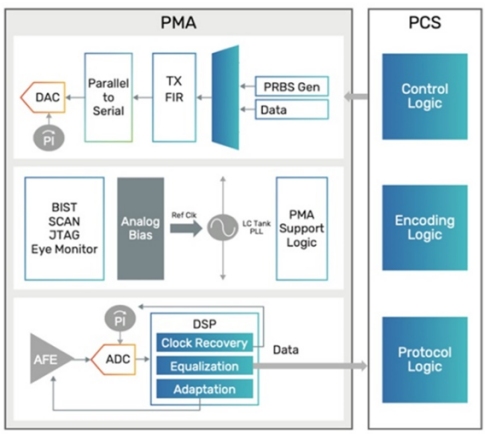

图2:Piper——Cadence面向PCIe 7.0的PHY IP

图3:业界首款面向PCIe 7.0的IP子系统

这适用于哪个市场?

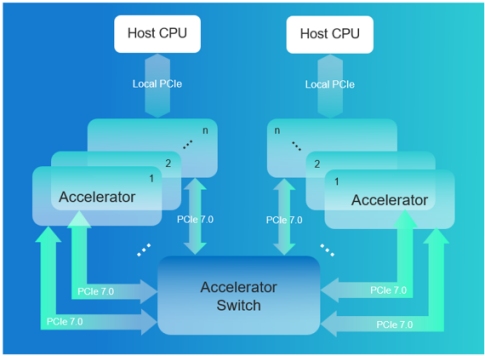

如今,加速计算已成为主流,PCIe链路在系统中的作用随之愈发凸显。在服务器或计算集群内,要跨多个图形处理器(GPU)或加速器扩展复杂的计算任务,实现GPU之间的直接通信至关重要。业内逐渐认识到,要实现高性能计算,需要可扩展的开放式架构。随着AI和数据密集型应用的发展,对这种技术的需求可能增加,因此PCIe 7.0将成为下一代接口IP的关键部分。

下图展示了PCIe 7.0的潜在用例。

图4:PCIe 7.0用例

光纤链路为何如此重要?

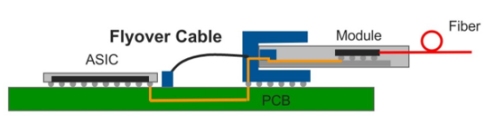

如今,训练AI/ML模型需要多个数据中心协作,而这些数据中心的地理位置又越来越分散,因此要求光纤网络能够有效应对因传输距离变长而导致带宽增加的问题。然而,将信号从A点传输到B点便已消耗掉所有预算功耗,已没有足够的功耗来运行实际的CPU和GPU,因此光模块很快就会遇到功耗瓶颈。在这种情况下,非重定时的线性拓扑结构便可发挥所长。与传统的基于数字信号处理 (DSP) 的重定时光学解决方案相比,线性可插拔光学器件 (LPO) 链路可显著降低模块功耗和延迟,这对于提升AI性能至关重要。而且,由于功耗和冷却要求有所降低,从基于DSP的解决方案切换到LPO还可显著节约成本,减少开支,但于此同时,重定时器/DSP将不再适用,而是需要一个功能强大的高性能ASIC来驱动光学器件。

为了展示Cadence IP的稳健性,我们演示了面向PCIe 7.0的子系统测试芯片板能够通过外部环回模式配置的非重定时光电链路成功发送和接收128GT/s信号,并留有多个数量级的裕度。

图5:ASIC驱动线性光学器件示例

合规是关键

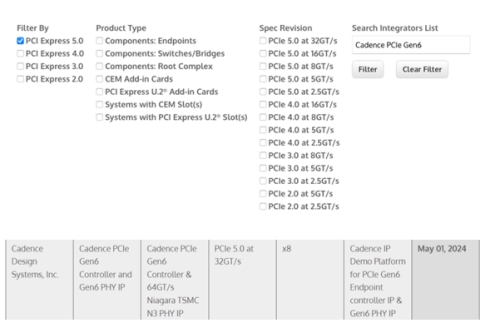

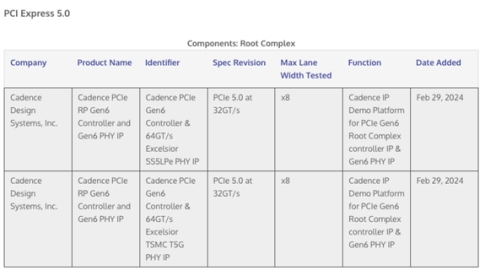

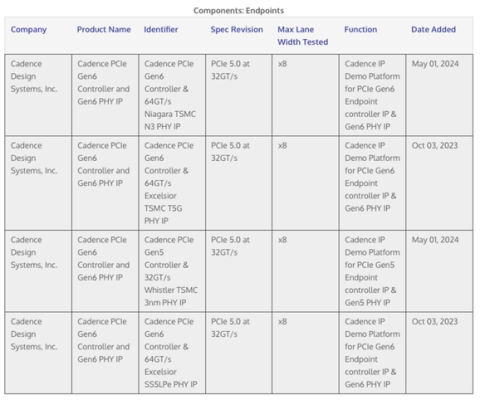

对PCIe 6.0,目前官方合规计划尚未启动。这是SIG的常规做法,即在规范获批几年后启动合规计划,以便生态系统有充足的时间来准备初始产品,并让测试和设备供应商有足够的时间来启动和运行他们的硬件/软件。目前,PCIe 6.0只能通过最高PCIe 5.0级别(SIG支持的最高官方合规性测试套件)的官方认证。我们已经向SIG提交了针对多个工艺节点的PCIe 6.0 IP子系统解决方案,它们均被列为合规产品。您可以登录pcisig.com网站,在Developers->Integrators列表下查询,具体如下所示:

PCI-SIG开发者大会的其他看点

在6月12日和13日举办的PCI-SIG开发者大会上,Cadence进行了以下演示:

- Cadence面向PCIe 7.0的IP通过非重定时光学器件发送和接收128GT/s信号的强大性能

- 使用示波器测量Cadence面向PCIe 7.0的IP的功能,详细说明其稳定的电气性能和裕度

- Cadence面向PCIe 6.0接口的IP的可靠性,使用测试设备表征PHY接收器的质量

- Cadence面向PCIe 6.0的PCI-SIG兼容IP子系统,在功耗和性能方面进行了优化

作为PCI Express领域的领军人物,Cadence的Anish Mathew了分享他对“UIO ECN对PCIe控制器设计和性能的影响”这个重要话题的宝贵见解,重点介绍了Cadence设计团队在实现这一目标方面所取得的进展。

图6:Cadence UIO实现总结

总结

Cadence于2023 PCI-SIG开发者大会期间展示了PCIe7.0-Ready IP,将继续引领PCIe IP的开发,面向PCIe 7.0提供支持先进节点的完整解决方案。预计这些解决方案将于明年初发布。Cadence以PCI-SIG的成员身份为豪,将继续为市场提供包括PHYs、控制器、软件和验证IP在内的完整解决方案,并大量投资于PCIe项目。Cadence是首家提供面向PCIe 3.0、4.0、5.0和6.0的完整子系统解决方案的IP供应商,拥有业内领先的功耗、性能、面积 (PPA)。我们很荣幸能够继续提供面向PCIe 7.0的最新IP子系统解决方案,为PPA和上市时间设定新的基准。

Related Semiconductor IP

- Very fast VMAF accelerator

- AV1 Video Encoder IP

- TSMC CLN3FFP HBM4 PHY

- CAN 2.0/CAN FD IP core

- Multi-Channel AXI DMA Engine