TSMC CLN3FFP HBM4 PHY

IGAHBMZ03A is a High Bandwidth Memory 4 Physical Layer (HBM4 PHY) that is compliant with JEDEC HBM4 DRAM Specification JESD270-4.

Overview

IGAHBMZ03A is a High Bandwidth Memory 4 Physical Layer (HBM4 PHY) that is compliant with JEDEC HBM4 DRAM Specification JESD270-4. Fabricated in the TSMC 3 nm Advanced process node (N3P), it supports the data rate up to 12 Gbps per data pin in the DDR PHY Interface (DFI)-like 1:4 clock frequency ratio (HBM4 controller clock: WDQS = 1:4). The signal and power integrity is analyzed by the GUC design flow to meet all signal and power requirements.

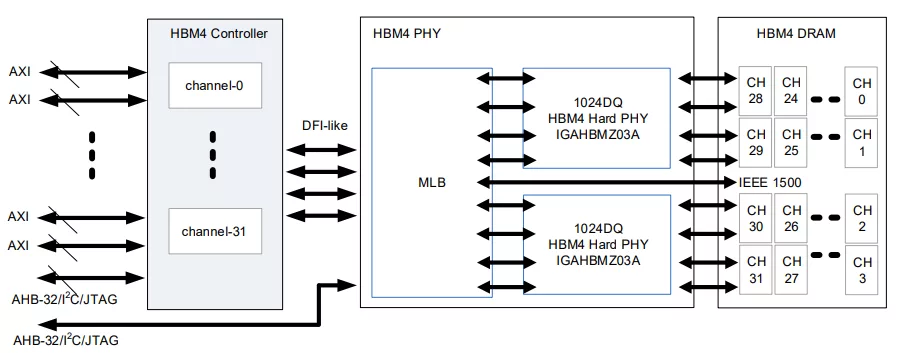

GUC HBM4 PHY includes a hard PHY and a Register Transfer Level (RTL) soft module. The hard PHY, IGAHBMZ03A, includes Command Address (CA) modules, data modules, IO pads, a Phase-Locked Loop (PLL), and Delay-Locked Loops (DLLs). The RTL soft module, also called Miscellaneous Logic Block (MLB), included to work with the hard PHY for functions, such as the training logic, the register controller interface, the Built-In Self-Test (BIST) logic, and the IEEE 1500 function logic.

Key features

- HBM4 data rate: up to 12 Gbps

- DFI-like 1:4 clock frequency ratio (HBM4 controller clock: WDQS = 1:4)

- Only Burst Length 8

- AWORD/DWORD bus parity

- Programmable parity latency

- HBM4 Data Bus Inversion (DBI)

- 64DQ ECC/SEV per channel

- HBM4 Hard PHY delivered as a hard macro including IO, PLL, and DLL

- Internal Loopback and WRITE/READ BIST

- HBM4 loopback test, including MISR and LFSR modes

- IEEE 1500 Instruction

- HBM4 lane repairs with redundant pins for row/column/data

- HBM4 Duty Cycle Adjuster (DCA) and Duty Cycle Monitor (DCM) training.

- HBM4 AWORD write eye/VREF/perbit training training

- HBM4 WDQSK2CK training

- HBM4 DWORD write/read eye/VREF/perbit training

- Broken lane detect and repair

- DLL compensation to overcome VT variation

- HBM4 DWORD write eye retrain to overcome Device VT variation

Technology

- Process: TSMC 3 nm 0.75 V/1.2 V CMOS LOGIC FinFET Advanced Process

- Special layer & device: SVT, LVT, LVTLL, ULVT, ULVTLL and ELVT

- Metal scheme: 1P17M (1Xa_h_1Xb_v_1Xc_h_1Xd_v_1Ya_h_1Yb_v_4Y_hvhv_4Yy2Z)

Block Diagram

Applications

- For applications with high performance & high bandwidth memory, such as AI/ HPC.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is TSMC CLN3FFP HBM4 PHY?

TSMC CLN3FFP HBM4 PHY is a Single-Protocol PHY IP core from Global UniChip Corp. (GUC) listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.