RSA

All offers in

RSA

Filter

Compare

27

RSA

from

12

vendors

(1

-

10)

-

100% Secure Cryptographic System for RSA, Diffie-Hellman and ECC with AMBA AHB, AXI4 and APB

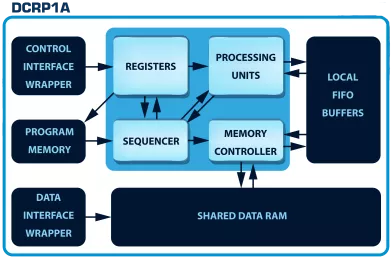

- The DCRP1A - CryptOne IP is a 100% secure cryptographic system

- CryptOne is a fully scalable, hardware-accelerated cryptographic system

- Designed for next-generation SoCs, FPGAs, and secure embedded systems, it delivers 100% secure asymmetric cryptography acceleration for demanding applications.

-

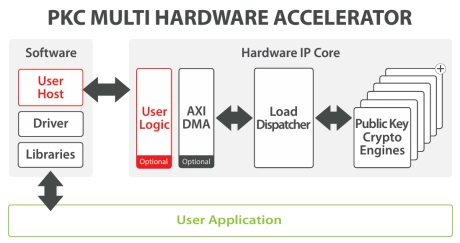

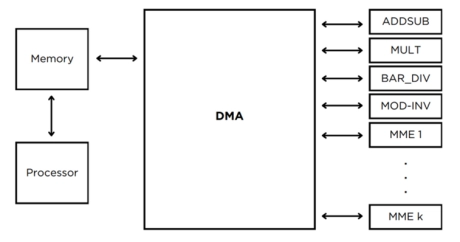

PKC Multi Hardware Accelerator IP

- The PKC Multi hardware accelerator is a secure connection engine that can be used to offload the compute intensive Public Key operations (Diffie-Hellman Key Exchange, Signature Generation and Verification), widely used for High-performance TLS Handshake.

-

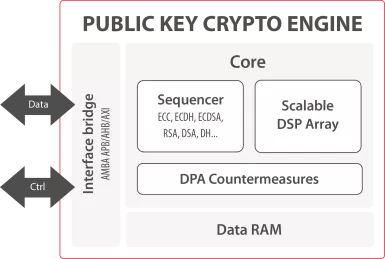

Public Key Crypto Engine

- The Public Key Crypto Engine is a versatile IP core for hardware offloading of all asymmetric cryptographic operations.

- It enables any SoC, ASIC and FPGA to support efficient execution of RSA, ECC-based algorithms and more.

- The IP core is ready for all ASIC and FPGA technologies.

-

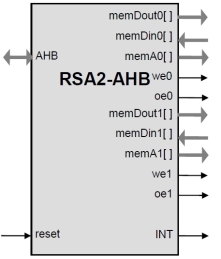

RSA2-AHB Accelerator Core with AHB Interface

- The core implements the exponentiation operation of the RSA cryptography Q = Pk.

- The operands for the exponentiation: k and P as well as the modulus are programmed into the memory and the calculation is started.

- Once the operation is complete, the result Q can be read through the AHB interface.

-

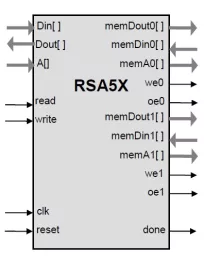

Scalable RSA and Elliptic Curve Accelerator

- The core implements the exponentiation operation of the RSA cryptography Q = Pk.

- The operands for the exponentiation: k and P as well as the modulus are programmed into the memory and the calculation is started.

- Once the operation is complete, the result Q can be read through the interface.

-

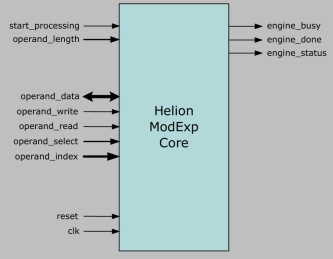

Modular Exponentiation Core

- Fully synthesisable RTL source code

- VHDL/Verilog testbench with test vectors

- User documentation

-

RSA Keygen IP Core

- RSA Keygen IP Cores perform key generation in compliance with the RSA Key Pair Generation specifications defined in 'FIPS 186'.

- This standard specifies methods for generating RSA key pairs.

- RSA Keygen IP Cores support key pair generation up to 4096 bits.

-

RSA IP Core

- RSA IP Cores perform digital signature generation and verification in compliance with the RSA (Rivest-Shamir-Adleman) Digital Signature Algorithm specifications defined in 'FIPS 186'.

- This standard specifies methods for digital signature generation and verification using the RSA Digital Signature Algorithm.

- RSA IP cores support bit lengths from 256 to 4096.

-

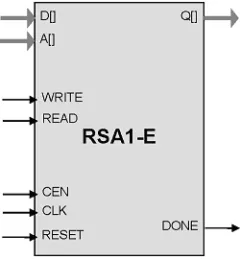

RSA Public Key Exponentiation Accelerator

- Small size: RSA1-E starts from less than 10K ASIC gates (intermediate result storage memory required; size depends on the core configuration)

- Implements the computationally demanding parts of RSA public key cryptography for long life battery powered applications

- Support for RSA binary fields of configurable bit sizes up to 2048

- Microprocessor-friendly interface

-

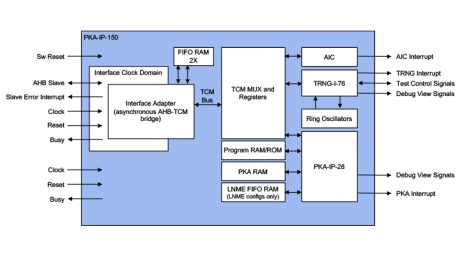

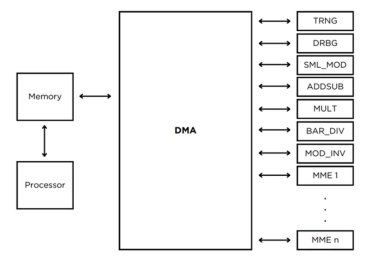

RSA/ECC Public Key Accelerators with TRNG and AHB

- Up to 4160-bit modulus size for RSA & 768-bit modulus for prime field ECC operations

- Public key signature generation, verification and key negotiation with little involvement of host

- NIST CAVP compliant for FIPS 140-3