kasumi IP

Filter

Compare

14

IP

from

5

vendors

(1

-

10)

-

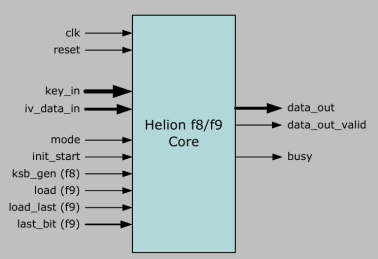

3GPP KASUMI f8 and f9 cores

- The Helion 3GPP KASUMI cores perform the f8 confidentiality and f9 integrity algorithms required to provide data security within the GSM/EDGE and UMTS mobile communication standards.

- Both algorithms are based on the KASUMI 64-bit block cipher which uses a 128-bit key. The KASUMI algorithm was designed by the Security Algorithms Group of Experts (SAGE) within ETSI, and is an optimised version of the MISTY1 block cipher originally developed by Mitsubushi Electric Corporation of Japan. Within ETSI, the f8 and f9 algorithms are now known as UEA1 and UIA1 respectively.

-

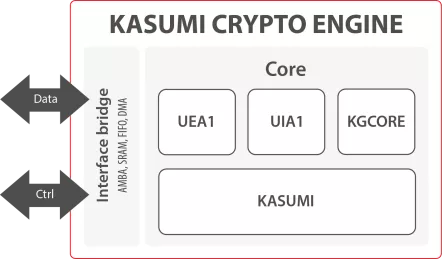

KASUMI Crypto Engine

- The KASUMI IP core is 3GPP confidentiality and integrity algorithms (UEA1/UIA1) stream cipher for telecommunication applications, requiring high performance with reduced silicon resources.

- It is optimized for maximum throughput and minimum latency.

-

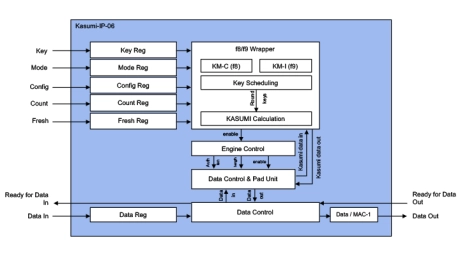

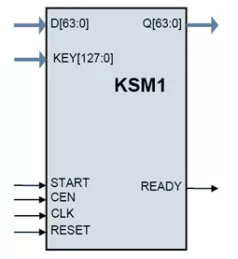

3GPP Kasumi Accelerators

- Wide bus interface (64-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware.

- Modes Kasumi

- Algorithms f8 and f9.

- Fully synchronous design.

- Low Speed, High Speed versions.

-

Kasumi Encryption Core

- Encryption using the Kasumi Block Cipher Algorithm

- Since all practical uses of Kasumi utilize only the encryption operation, decryption is not part of the core

- High throughput: up to 3 Gbps in 65 nm process

- Small size: from 5.5K ASIC gates

-

Multipurpose Security Protocol Accelerator

- Highly configurable security accelerator

- Support for all ciphers, hashes and MAC algorithms used in major protocols such as IPsec, SSL/TLS/DTLS, Wi-Fi, 3GPP LTE/LTE-A, SRTP, MACsec

- Cipher algorithms: AES, DES/3DES, ChaCha20, MULTI2, KASUMI, SNOW 3G, ZUC

- Cipher modes: ECB, CBC, CTR, OFB, CFB, f8, XTS, UEA1, UEA2, 128-EEA1, 128-EEA2, 128-EEA3

-

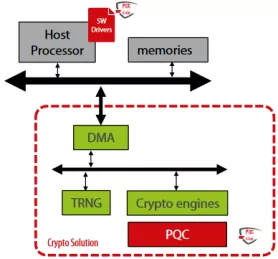

Crypto Coprocessor with integrated Post-Quantum Cryptography IPs

- The Crypto Coprocessors are a hardware IP core platform that accelerates cryptographic operations in System-on-Chip (SoC) environment on FPGA or ASIC.

- Symmetric operations are offloaded very efficiently as it has a built-in scatter/gather DMA. The coprocessors can be used to accelerate/offload IPsec, VPN, TLS/SSL, disk encryption, or any custom application requiring cryptography algorithms.

-

Multipurpose Security Protocol Accelerator - Functional Safety ASIL B support

- Highly configurable security accelerator

- Support for all ciphers, hashes and MAC algorithms used in major protocols such as IPsec, SSL/TLS/DTLS, Wi-Fi, 3GPP LTE/LTE-A, SRTP, MACsec

- Cipher algorithms: AES, DES/3DES, ChaCha20, MULTI2, KASUMI, SNOW 3G, ZUC

- Cipher modes: ECB, CBC, CTR, OFB, CFB, f8, XTS, UEA1, UEA2, 128-EEA1, 128-EEA2, 128-EEA3

-

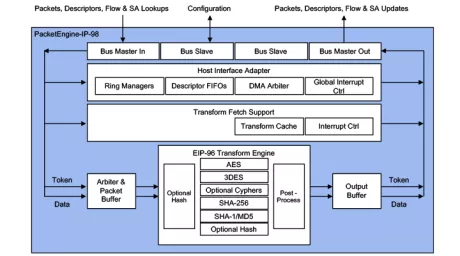

Multi-Protocol Engine with Classifier, Look-Aside, 5-10 Gbps

- Protocol aware IPsec, SSL, TLS, DTLS, 3GPP and MACsec Packet Engine with virtualization, caches classifier and Look-Aside interface for multi-core application processors

- 5-10 Gbps, programmable, maximum CPU offload by classifier, supports new and legacy crypto algorithms, AMBA interface

- Supported by Driver development kit, QuickSec IPsec toolkit, Linaro ODP, DPDK, Linux Crypto

-

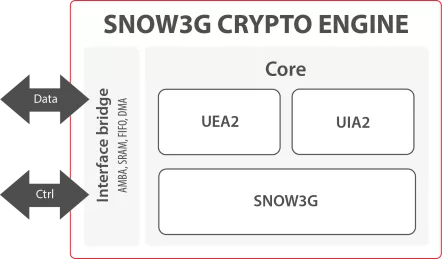

SNOW3G Crypto Engine

- ASIC and FPGA

- ETSI specifications compliant

- Supports:

- Data interface: AMBA (AXI/AHB) with optional DMA