PCI Express Multichannel DMA IP

Filter

Compare

6

IP

from

2

vendors

(1

-

6)

-

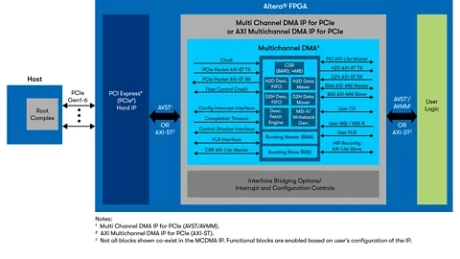

Multichannel DMA Intel FPGA IP for PCI Express*

- The Multichannel DMA IP for PCI Express provides high efficiency, speed, and configuration flexibility to support various applications from HPC, cloud, networking, to embedded

- With support for up to 2048 channels and Linux-based PCIe drivers provided, this low latency, low resource utilization solution is essential in handling movements of large volumes of data to optimize system performance.

-

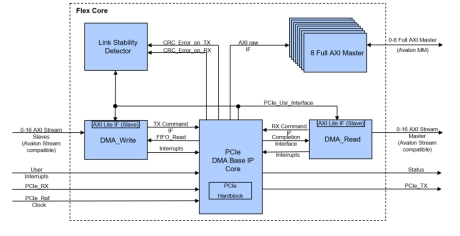

Multi-Channel Flex DMA IP Core for PCI Express

- The Multi-Channel DMA IP Core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- Up to 16 independent AXI Stream Slaves write DMA Data to the Host. Up to 16 AXI Stream Masters read DMA Data from the Host and present it to the User Logic.

- Each channel operates on a separate memory area. Additional 8 AXI4 Masters are available to interface full AXI or AXI-Lite peripherals with the Host.

-

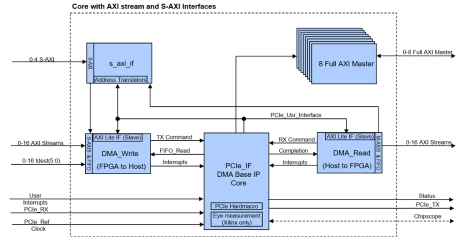

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

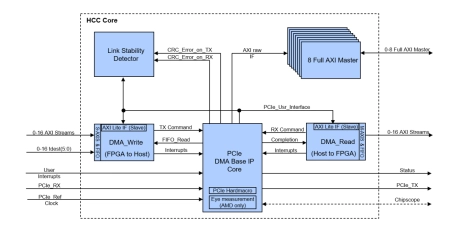

High Channel Count DMA IP Core for PCI-Express

- The High Channel Count (HCC) DMA IP core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- This IP addresses continuous streaming applications from up to 64 different data sources. Each channel is able to transmit data into a separate memory area.

- Up to 16 AXI Stream masters read DMA Data from the host and present it to the user logic. Additional 8 AXI4 masters are available to interface full AXI or AXI-Lite peripherals with the host.

-

R-Tile PCIe Hard IP

- R-Tile is a FPGA companion tile that supports configurations up to PCIe 5.0 x16 in Endpoint (EP), Root Port (RP), and Transaction Layer (TL) Bypass modes

- PCIe 3.0, 4.0, and 5.0 configurations are natively supported

- R-Tile also supports up to 16 SerDes channels through a PHY Interface for PCIe (PIPE) 5.1.1 in SerDes Architecture mode.

-

Intel® FPGA IP for PCIe

- PCI Express (PCIe*) protocol is a high-performance, scalable, and feature-rich serial protocol with data transfer rates from 2.5 gigatransfers per second (GT/s) to 32 GT/s and beyond

- Intel® FPGA Intellectual Property (IP) for PCIe continues to scale as the PCI-SIG organization delivers next-generation specifications

- Intel has been a member of PCI-SIG since 1992, and with each new generation of silicon, Intel continues to participate in PCI-SIG Compliance Workshops to ensure interoperability and conformance with current industry standards.