AXI Bridge with DMA for PCIe IP Core

The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a mix of multiple industry standard AXI Interfaces.

Overview

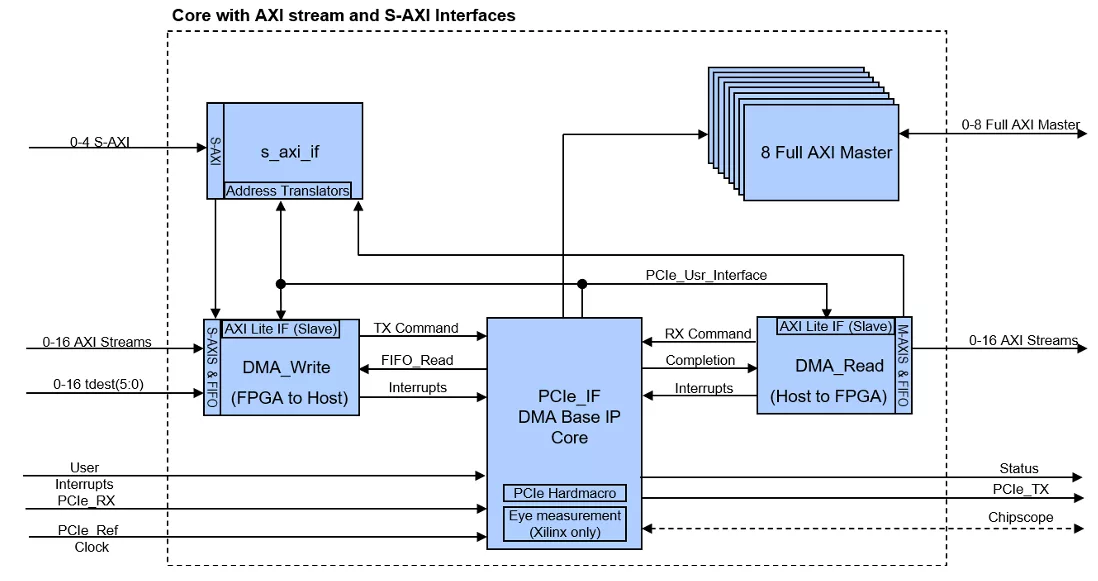

The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces. AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

This IP core enables the developer to build complex PCI Express endpoints with no specific PCI Express protocol know-how. The user only transmits or receives payload data and does not have to assemble valid PCI Express packets. A powerful kernel mode device driver is shipped with the IP for Windows or Linux operating systems to ensure easy software integration of the core.

Key features

- Lowest logic resource count in the industry

- Utilizes built-in HardFIFOs (AMD devices only)

- Multi-channel architecture

- Continuous high throughput data streaming

- Non-blocking approach, an incomplete AXI Stream packet does not block other AXI interfaces

- Up to 4 S-AXI interfaces for AXI2PCIe bridge applications (incl peer to peer applications) with up to 6 AXI BARs and dynamic address translation registers

- Up to 16 AXI Stream Slave interfaces

- Up to 16 AXI Stream Master interfaces

- Up to 8 AXI Masters to interface user registers

- User transmits / receives only user data without PCIe protocol knowledge

- Built in completion sorting: S-AXI read requests are answered always in the requested order

- Tandem, MSI and MSI-X supported

- Based on AMD / Lattice integrated PCI-Sig compliant PCIe Block (HardIP)

- Link speed Gen 1-4, link widths x1-x8

Block Diagram

What’s Included?

- Encrypted VHDL Source Code for easy Designflow integration

- Comprehensive User Guide

- Reference Design

- Windows / Linux Driver Package (Option)

- PCI-Express Testbench with High Speed simulation mode

- Technical support

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is AXI Bridge with DMA for PCIe IP Core?

AXI Bridge with DMA for PCIe IP Core is a Protocol Bridge IP core from Smartlogic GmbH listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.