HD-PLC IP

Filter

Compare

26

IP

from

16

vendors

(1

-

10)

-

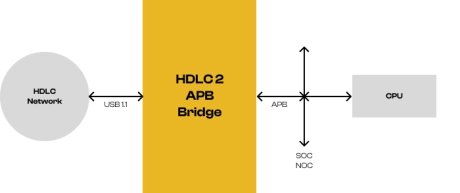

HDLC frame to APB bridge

- HDLC frame to APB bridge , is cable of receive and transmit of HDLC frame .

- The module is accessed through an APB slave from the host side.

-

Used for controlling HDLC/SDLC transmission protocols

- Two separate receiver and transmitter interfaces.

- Two separate, configurable FIFO buffers for receiver and transmitter

- Bit stuffing and unstuffing

- Address recognition for receiver and address insertion for transmitter

-

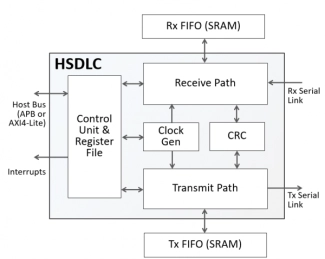

HDLC & SDLC Protocol Controller

- The HSDLC IP core implements a controller for the High-Level Data Link Control (HDLC) and the Synchronous Data Link Control (SDLC) protocols.

- It is based on the Intel® 8XC152 Global Serial Channel (GSC) working in SDLC mode, and adds features to support HDLC or proprietary frame transmission under host processor control.

- The core operates as a peripheral to a host processor, and is easy to integrate with both modern and legacy processors.

-

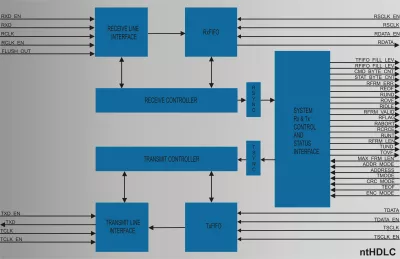

Single Channel HDLC Controller

- Single port synchronous serial line interface.

- Flag/Abort Generation/Detection.

- Zero Insertion/Deletion.

- Non-octet alignment detection.

-

HDLC Framer

- Best-in-Class size and performance, supports many thousands of channels.

- Supports bit-synchronous and byte-synchronous HDLC.

- Generates/Accepts data for multiple independent TDM HDLC streams. Generates/Removes flag characters to delineate HDLC frames.

- Inserts/Removes HDLC bit or byte stuffing. Provides variable width data output.

-

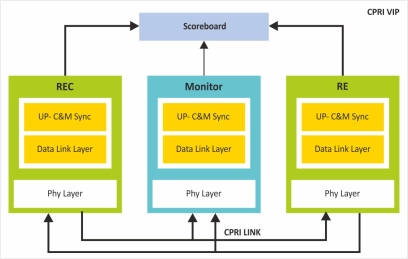

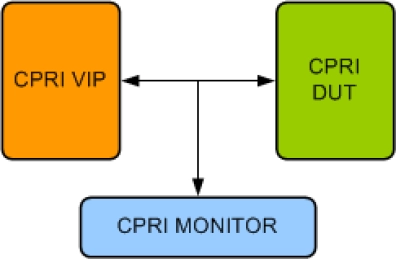

CPRI Verification IP

- Compliant with CPRI Specification V4.2/V5.0/V6.0/V6.1/V7.0

- Complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

-

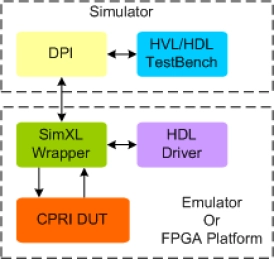

CPRI Synthesizable Transactor

- Compliant with CPRI Specification V4.2, V5.0, V6.0, V6.1 and V7.0.

- Supports complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

-

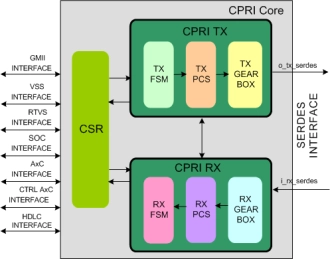

CPRI CONTROLLER IIP

- Compliant with CPRI Specification V4.2, V5.0, V6.0, V6.1 and V7.0.

- Complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

-

CPRI Verification IP

- Fully compliant to CPRI specification V7.0 with backward compatibility

- Supports following line bit rates of CPRI specifications

- 614.4 Mbit/s, 1228.8 Mbit/s, 3072.0 Mbit/s, 4915.3 Mbit/s, 6144.0 Mbit/s, 9830.4 Mbit/s, 8110.08 Mbit/s, 10137.6 Mbit/s, 12165.12Mbit/s

- 614.4 Mbit/s, 1228.8 Mbit/s, 3072.0 Mbit/s, 4915.3 Mbit/s, 6144.0 Mbit/s, 9830.4 Mbit/s, 8110.08 Mbit/s, 10137.6 Mbit/s, 12165.12Mbit/s

- Supports 8B/10B and 64B/66B line coding and scrambling/ descrambling and RSFEC.