Overview

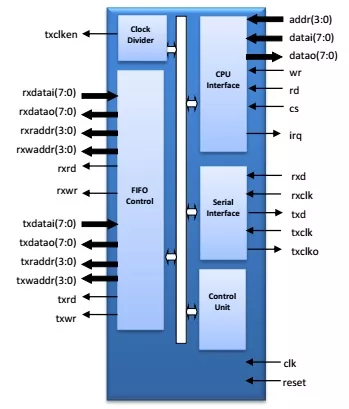

The DHDLC IP Core provides versatile support for a widely used HDLC transmission protocol. It manages the bit stuffing process, both address appending and detection. And if it’s not enough, let’s just mention that this Core supports CRC16 and CRC32 computation. Increased system performance and reduced CPU overload is a must be, thanks to the presence of separate receiver and transmitter FIFO buffers, maskable interrupt and DMA interface request. The DHDLC is a fully scalable IP Core, which makes it a perfect solution for both hi-end and deeply embedded projects. It’s tailored to your project needs and can be provided with: small 8-bit SRAM-like interface, 32-bit full AXI4 slave interface with burst support, AXI4Lite interface, AHB and APB slave interfaces. The optional Frame Status Buffer stores information about frames size and error conditions. Moreover, the size of the receiver and transmitter FIFO buffers is configurable. You can also easily remove unused features before the synthesis process. All that and much more make the DHDLC an ideal solution for very popular higher level protocol implementations like e.g. PPP (Point-to-Point), X.25, V.42, LAB-B, SDLC, ISDN and many others.

Provider

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about HDLC IP core

One not-so-glamorous but vitally important use for CAST digital IP cores is to replace obsolete parts. Many of our cores can provide the answer if you’re maintaining a legacy system and need to make your own FPGA for a discrete part that was discontinued years ago, or perhaps consolidating a working but ancient board design into a single new chip.

Build safety-critical automotive, aeronautic, space and other systems with the Functional Safety RISC-V Processor IP core from CAST and PolarFire® FPGAs.

D32PRO is one of the newest 32-bit CPUs available on the market. It’s been designed by Digital Core Design, IP Core provider and SoC design house from Poland, responsible e.g. for the world’s fastest or world’s smallest 8051 CPU. DCD launched more than 70 different architectures since 1999, which have been implemented in more than 300 000 000 electronic devices, that’s why one can be sure that quite considerable experience stands behind the D32PRO.

This paper describes a unique approach for developing drivers using hardware abstraction and standard APIs for hardware and software interfaces.

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP