Digital Imaging IP

Filter

Compare

23

IP

from

12

vendors

(1

-

10)

-

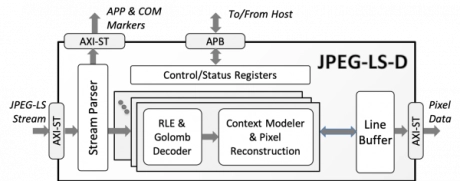

Lossless & Near-Lossless JPEG-LS Decoder

- The JPEG-LS-D core implements a highly efficient and low-power, lossless and near-lossless image decompression engine that is compliant to the JPEG-LS, ISO/IEC 14495-1 standard.

- The decoder core can decompress any JPEG-LS stream or JPEG-LS payload of image container formats, such as DICOM (Digital Imaging and Communications in Medicine).

-

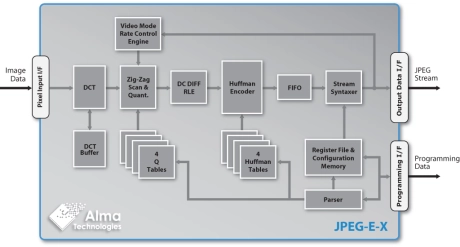

8/10/12-bit Extended JPEG Encoder with Optional Video Rate Control

- The JPEG-E-X core is a standalone and high-performance 8-bit Baseline and 10/12-bit Extended JPEG encoder for still image and video compression applications.

- Full compliance with the Baseline and the Extended Sequential DCT modes of the ISO/IEC 10918-1 JPEG standard makes the JPEG-E-X core ideal for interoperable systems and devices.

- The produced JPEG streams can also conform to the Digital Imaging and Communications in Medicine (DICOM) requirements.

-

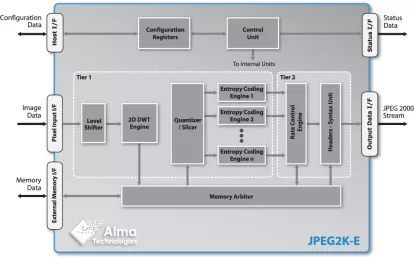

JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- ISO/IEC 15444-1 JPEG 2000 Image Coding System Compliance

- Programmable JPEG 2000 Encoding Options

- Smooth System Integration

-

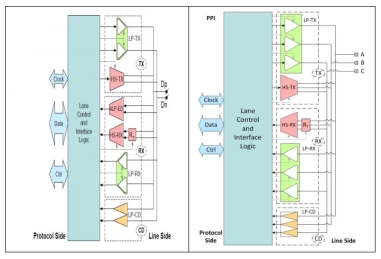

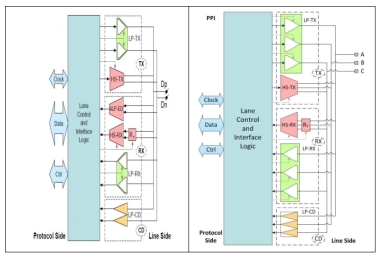

MIPI C-PHY℠ v2.0 + D-PHY℠ v2.5 Combo IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

MIPI D-PHY℠ v2.5 IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

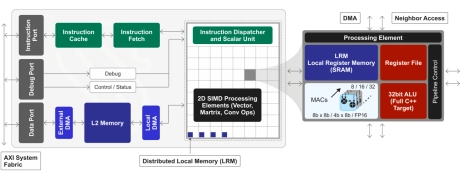

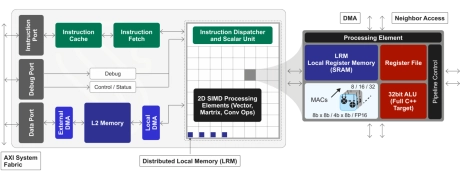

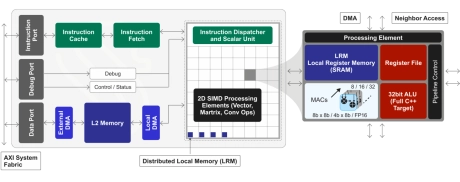

GPNPU Processor IP - 32 to 864TOPs

- 32 to 864TOPs

- (Dual, Quad, Octo Core) Up to 256K MACs

- Hybrid Von Neuman + 2D SIMD matrix architecture

- 64b Instruction word, single instruction issue per clock

- 7-stage, in-order pipeline

- Scalar / vector / matrix instructions modelessly intermixed with granular predication

-

-

-

Low-Power ISP

- The Image Signal Processing (ISP)-- ISI700 receives camera sensor data via the 4-channel DVP interface

- It is designed for multi-camera, multi-exposure high dynamic range (HDR) image signal processor (ISP) for the mid- to high-end consumer and surveillance market

- The ISI700 offers the following functions: It brings advanced imaging technologies and chromatic aberration correction to provide unrivalled image quality and support to a large number of HDR sensor formats

-

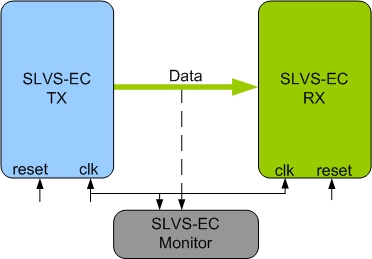

SLVS-EC Verification IP

- Full SLVS-EC transmitter device and receiver device functionality.

- SLVS-EC supports version 2.0 specification.

- Supports the following system topologies between CIS and DSP

- Basic Topology