JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

The JPEG2K-E core is a still image and video encoder that implements Part 1 of the JPEG 2000 standard.

Overview

The JPEG2K-E core is a still image and video encoder that implements Part 1 of the JPEG 2000 standard. It offers up to 16-bit per component Numerically Lossless and Lossy compression, including an advanced - high-quality and extremely accurate - rate control functionality. The JPEG2K-E can also optionally include support for single-component Multiple Quality Layers encoding in LRCP progression order.

The JPEG 2000 compression standard offers an advanced quality and feature set, lending itself to a wide range of uses from digital cameras through to space imaging and other key sectors. Full compliance to the ISO/IEC 15444-1 JPEG 2000 standard makes the JPEG2K-E core ideal for interoperable systems and devices.

The JPEG2K-E supports up to 64K x 64K image resolution using up to 8K x 8K tiles. It is a highly scalable IP before synthesis regarding encoding throughput and the corresponding silicon implementation area. The JPEG2K-E includes also an advanced post-compression, rate-distortion optimized, rate control engine which provides full control over the required bandwidth on the JPEG 2000 stream output. The bitrate of the JPEG 2000 stream can be accurately adjusted while, at the same time, preserving the maximum image fidelity that is possible within the available bandwidth constraints.

The JPEG2K-E core implements a simple but yet flexible, requests based, external memory interface with independent read and write data paths. This makes the JPEG2K-E independent of memory type supporting, for example, operation with SRAM, SDRAM, DDR, DDR2 and DDR3 types of memory. JPEG2K-E is designed to be tolerant to memory delays and latencies, which may be present on shared memory system architectures.

The core is designed with simple, fully controllable and FIFO-like, streaming input and output interfaces. Being carefully designed, rigorously verified and silicon-proven, the JPEG2K-E is a reliable and easy-to-use and integrate IP.

Key features

- ISO/IEC 15444-1 JPEG 2000 Image Coding System Compliance

- Up to 65535 x 65535 image resolution

- Up to 8192 x 8192 tile resolution

- 1, 3 and 4 component images

- Up to 16-bit per component

- 4:4:4, 4:2:2, 4:1:1 and 4:2:0 chroma sampling formats

- Numerically lossless or lossy compression

- Advanced rate control engine

- Single or multiple quality layers encoding

- CPRL or LRCP (single component only) progression order

- Error resilient encoding features

- Standard compliant code stream (JPC) or file (JP2) output

- Programmable JPEG 2000 Encoding Options

- Image and pixel input format (frame and tile size, number of components, pixel depth, chroma sampling format, and input scan order)

- Wavelet filter type (5/3 or 9/7) and number of wavelet transform levels

- Code-block size (64 or 32 or 16 on each dimension)

- Quantization tables

- Entropy coding switches (reset, segmark)

- Number of quality layers (single component only, up to 30)

- Output bitrate (per quality layer)

- Progression order and JPEG 2000 output format (proprietary or JPC or JP2)

- Smooth System Integration

- Full abstraction of the internal implementation details and the JPEG 2000 complexity from the IP top level I/O and its operation

- Simple, microcontroller like, programming interface

- High-speed, flow controllable, streaming I/O data interfaces

- Simple and FIFO like

- Avalon-ST compliant (ready latency 0)

- AXI4-Stream compliant

- Low requirements in external memory bandwidth

- Flexible external memory interface

- Independent of external memory type

- Tolerant to latencies

- Allows for shared memory access

- Can optionally operate on independent clock domain

- Trouble-Free Technology Map and Implementation

- Fully portable, self-contained RTL source code

- Strictly positive edge triggered design

- D-type only Flip-Flops

- Safe CDC transfers when using more than one clock domain

- No special timing constraints required

- No false or multi-cycle paths within the same clock domain

- No CDC transfers that need to be constrained (all CDC paths can be excluded)

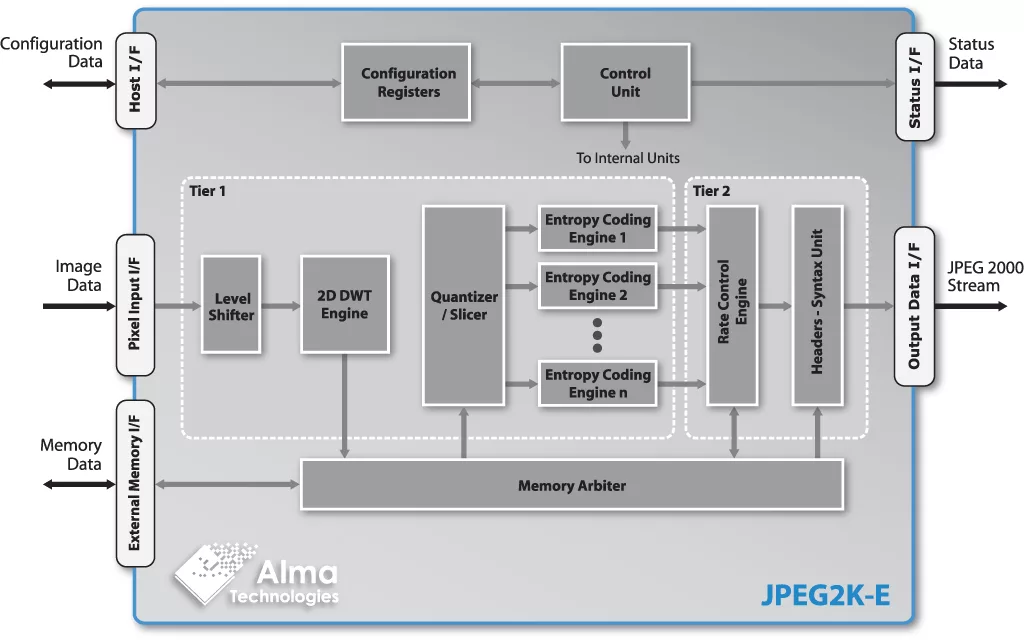

Block Diagram

What’s Included?

- Clear text VHDL RTL source for ASIC designs, or pre-synthesized & verified Netlist for Altera, Lattice, Microsemi and Xilinx FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Self checking testbench environment, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Image Conversion IP core

Nextreme Structured ASICs: An alternative for designing cost-optimized ARM926EJ processor-based embedded systems

Video Messaging for ARM7-based Cellular Chipsets.

Configurable Processors for Video Processing SOCs

Generating High Speed CSI2 Video by an FPGA

Viewpoint: Opportunity to win on different design fronts

Frequently asked questions about image conversion IP cores

What is JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression?

JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression is a Image Conversion IP core from Alma Technologies listed on Semi IP Hub.

How should engineers evaluate this Image Conversion?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Image Conversion IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.