DSP accelerator IP

Filter

Compare

35

IP

from

12

vendors

(1

-

10)

-

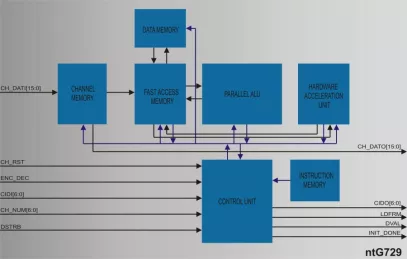

ITU-T G729A Voice Codec Hardware Accelerator

- Voice codec capable of multi-channel 8kbps voice compression based on ITU-T G729A standard.

- Selective Channel initialization.

- AMBA bus support for easy SoC integration.

- Best performance/silicon area ratio available in the industry.

-

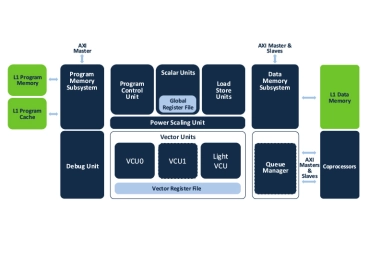

256 8-bit-MAC DSP core

- High performance vector signal processing and efficient control code processing

- 256 8-bit macs, or 128 16-bit macs, or 32-bit macs per cycle

- Flexible vector permute operations

- Maskable vector lanes

-

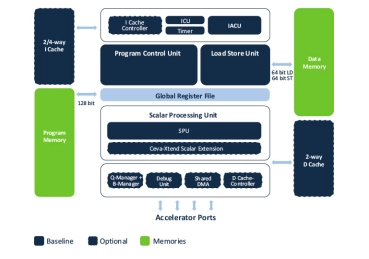

32 8-bit-MAC Vector DSP Core

- High performance vector signal processing and efficient control code processing

- 32 8-bit macs, or 16 16-bit macs, or 8 32-bit macs per cycle

- Flexible vector permute operations

- Maskable vector lanes

-

128 8-bit-MAC Vector DSP Core

- High performance vector signal processing and efficient control code processing

- 256 8-bit macs, or 128 16-bit macs, or 32-bit macs per cycle

- Flexible vector permute operations

- Maskable vector lanes

-

Quad MAC DSP core

- Four 16b macs/cycle or Two 32b macs/cycle

- 8/16/32/64 data types

- SIMD support

- High precision (upto 72 bit accumulation)

-

Vision AI DSP

- Ceva-SensPro is a family of DSP cores architected to combine vision, Radar, and AI processing in a single architecture.

- The silicon-proven cores provide scalable performance to cover a wide range of applications that combine vision processing, Radar/LiDAR processing, and AI inferencing to interpret their surroundings. These include automotive, robotics, surveillance, AR/VR, mobile devices, and smart homes.

-

-

DSP-enhanced ARC EMxD and HS4xD processors provide combined RISC + DSP processing for computation intensive applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

Tiny, Energy-efficient, MCU + DSP

- Dual 16b macs/cycle or One 32b macs/cycle

- 8/16/32/64 data types

- SIMD support

- High precision (upto 40 bit accumulation)

-

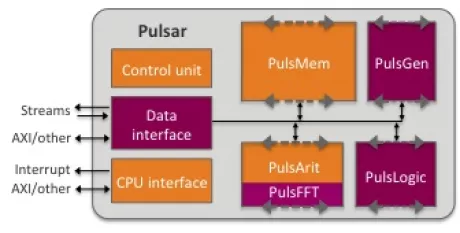

Scalable and Programmable Co-processor

- Hardware scalability to offer the best cost-performance trade-off

- Programmable Software-defined solution for flexible DSP components

- Enables complex DSP and high data-rate communication system design

- Can be optimized for FPGA and ASIC targets