Vendor:

Simpulse

Category:

DSP Core

Scalable and Programmable Co-processor

Simpulse’s Pulsar DSP IP Core is a scalable and programmable co-processor for the signal processing of complex embedded digital s…

Overview

Simpulse’s Pulsar DSP IP Core is a scalable and programmable co-processor for the signal processing of complex embedded digital signal processing (DSP) systems. Pulsar’s silicon intellectual property (IP) is a scalable processor architecture that perfectly allies hardware computational power with the flexibility of software.

Key features

- Hardware scalability to offer the best cost-performance trade-off

- Hardware complexity can be adapted to the application

- Low power solution (specialized hardware operator to reduce the power consumption)

- Highly parallel single instruction multiple data (SIMD) processor architecture

- Programmable Software-defined solution for flexible DSP components

- Flexible signal processing circuits with reduced development effort (20x lower than hard-wired design)

- Programmable Software signal processing core that avoids the development of dedicated hard-wired accelerators

- Easy support of standard revisions

- Easy product maintenance

- Easy design of multi-standard applications (multi-standard support: 4G/5G, LTE, DVB-T2, DVB-S2, …)

- Enables complex DSP and high data-rate communication system design

- Complex DSP algorithms management

- Complex vector processing optimization

- Very high system performance and computing power

- Can be optimized for FPGA and ASIC targets

- Easy migration from FPGA to ASIC

- FPGA prototyping before tape-out

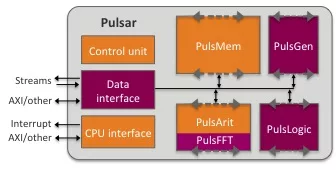

Block Diagram

Pulsar DSP IP Core block diagram

Benefits

- Pulsar DSP IP Core offers THE most flexible and reliable solution for the design of complex high-end signal processing electronic circuits

What’s Included?

- Pulsar RTL hardware design in synthesizable VHDL code

- Pulsar C++ bit and cycle accurate model available for very fast C++/VHDL/Verilog simulation (1000 time faster than synthesizable VHDL model)

- Associated development tools, comprising starting libraries, Makefile add-ons, sample codes and simulation platform

Specifications

Identity

Part Number

Pulsar DSP IP Core

Vendor

Simpulse

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

Simpulse

HQ:

France

Simpulse offers embedded Software-Defined Radio (SDR) solutions for innovative professional communication systems.

When environments are challenging and security primes, robust technology is needed to ensure secure and powerful data and video transmissions. Based on SDR technology, Simpulse’s radio links are the answer to professional applications that operate in highly mobile conditions and require a power-optimized, robust and secure solution.

We push the limits of current communication system design thanks to the scalable and programmable PULSAR SDR technology that offers a high level of flexibility and integration, and to advanced signal processing algorithms that improve robustness in presence of interferences and mobile channels.

Simpulse's flagship product, the SL100 mobile data-link modem, is dedicated to very long-range and highly mobile data transmissions. We also offer custom SDR modems that serve a great variety of specialized radio links. Typical applications include data and video radio links for various usages in drones, UAVs, robots, IoT concentrators, transportation, aerospace, public safety and defense.

The company was founded in January 2011 and is headquartered in Palaiseau, France.

Learn more about DSP Core IP core

Wireless 5G BTS Need Super DSP core... CEVA XC-12

Eric Esteve

CEVA-X1 DSP Core Targets Cellular IoT Opportunities

Oxford Digital Offers Small Audio DSP Core With Graphical Programming

icyflex: an ultra-low power DSP core for portable applications

The icyflex family of ultra low power 16/32-bit RISC processor cores developed by CSEM offers a flexible architecture that allows for different com-binations of control and DSP functionality. These processors target applications requiring long battery life at the same time as on-chip processing power. Three silicon-proven icyflex cores are available, consuming as little as 6 μW/MHz.

FPGA configures DSP core in imaging app

FPGA configures DSP core in imaging app

Frequently asked questions about DSP Core IP cores

What is Scalable and Programmable Co-processor?

Scalable and Programmable Co-processor is a DSP Core IP core from Simpulse listed on Semi IP Hub.

How should engineers evaluate this DSP Core?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DSP Core IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.