AHB PCI Bridge IP

Filter

Compare

8

IP

from

5

vendors

(1

-

8)

-

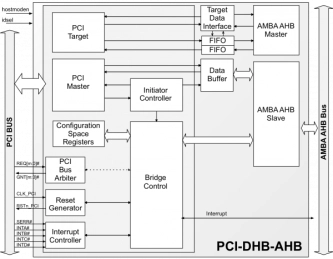

PCI - AMBA AHB Device/Host Bridge

- This PCI Host Bridge IP core enables data transfers between an AMBA® AHB host processor bus system and PCI bus based devices.

- The bridge supports Host Mode and Device Mode (selected by a dedicated input pin). In Host Mode, the bridge is in charge of PCI bus arbitration and generating the PCI reset signal.

-

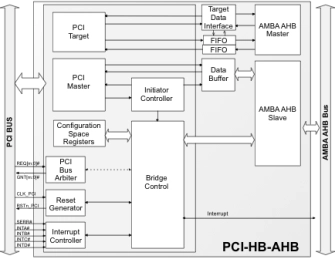

AMBA AHB to PCI Host Bridge

- Fully supports PCI specification 2.1 and 2.2 protocol.

- Supports AHB bus protocol.

- Downstream access transfer from AHB bus to PCI bus.

- Upstream access transfer from PCI bus to AHB bus.

-

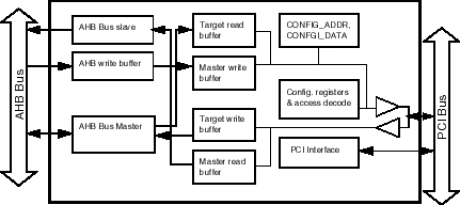

PCI to AMBA AHB Host Bridge

- This PCI Host Bridge IP core enables data transfers between an AMBA® AHB host processor bus system and PCI bus based devices.

- The bridge enables higher utilization of the bus’ available bandwidth by prefetching PCI data and buffering AHB data, and allows the host to initiate PCI accesses or to respond to transactions initiated by other PCI devices.

-

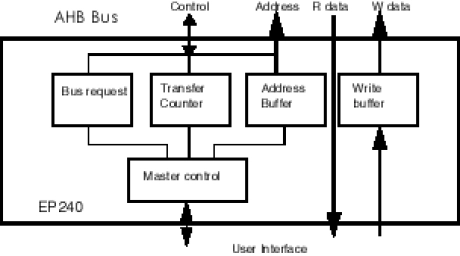

AMBA AHB Bus Master

- Supports AHB bus interface to the ARM CPU.

- User interface designed for high speed access to any slave devices on the AHB Bus.

- User specified single or burst data access on the AHB interface and user interface.

- Handles wait state insertion by any slave devices.

-

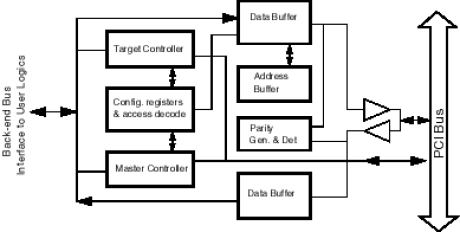

32-bit PCI Bus Master/Target

- Fully supports PCI specification 2.1 and 2.2 protocol.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Efficient back-end interface for different types of user devices.

-

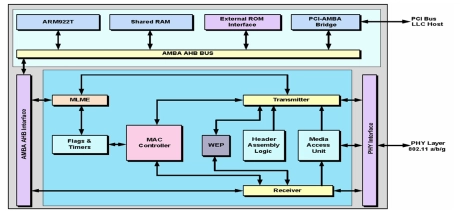

802.11 a b and g IEEE Standard - Wireless LAN

- The MAC core for Wireless LAN is compatible with 802.11 a b and g IEEE Standards.

- It is designed to handle packetized DSSS (Direct Sequence Spread Spectrum) and OFDM (Orthogonal Frequency Division Multiplexing) data transmissions; the software implementation supports all data rates.

- The MAC management or control functionality is implemented in firmware while the time critical functionality is implemented in hardware.

-

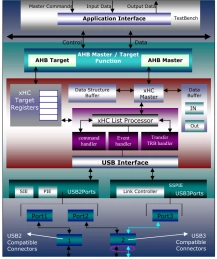

Super Speed USB 3.0 Extensible Host Controller xHCI

- The Super-Speed USB Host Controller is designed for flexibility, ease of use and provides ASIC/FPGA designers to implement a complete USB3.0 Host for 5 Gbps operation.

- The Host packet traffic can be explicitly routed and need not be broadcasted.

-

Configurable AMBA bus SoC platform

- Robust and fully synchronous single-edge clock designs

- Up to 125 MHz in FPGA and 400 MHz on 0.13 um ASIC technologies

- Fault-tolerant and SEU-proof version

- Symmetric Multi-processor support (SMP)