UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

Understand the role of the UCIe D2D Adapter in enabling reliable, scalable, multi-protocol die-to-die communication for chiplet architectures.

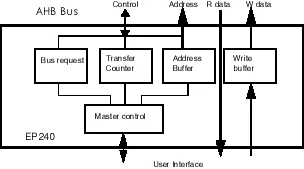

AMBA AHB Bus Master

Note: some files may require an NDA depending on provider policy.

AMBA AHB Bus Master is a Protocol Bridge IP core from Eureka Technology, Inc. listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.