AGI IP

Filter

Compare

136

IP

from

35

vendors

(1

-

10)

-

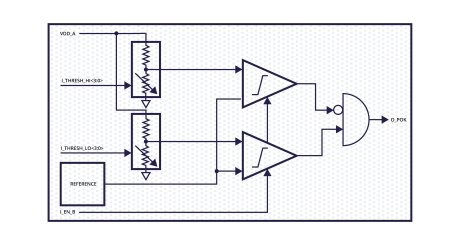

Power-OK Monitor

- The agilePOK is a Power OK monitor that consists of a voltage reference and comparators to set a programmable high and low threshold level for power supply integrity detection.

- The number of trigger outputs can be customized and each threshold can be adjusted during operation to support DVFS operation.

- This monitor can be used to detect loss of power or attacks to the power supply.

-

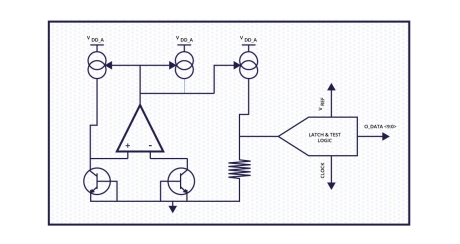

Temperature Glitch Detector

- The agileTGLITCH temperature monitor provides security and protection against side-channel attacks (SCAs) and tampering such as over/under temperature attacks and temperature glitching.

- The sensor provides digital outputs to warn (secure) processors of intrusion attempts. As a key part of the agileSCA TVC (Temperature, Voltage, Clock) security sensor can be tuned to your specifications.

-

Agile PQC Public Key Accelerator

- Agile IP comprised of HW/FW/SW, adaptable to future standards’ evolution

- Highly configurable IP can be tuned for specific applications with most optimal PPA

- Scalable PQC PKA IP complies with latest NIST PQC algorithms

-

-

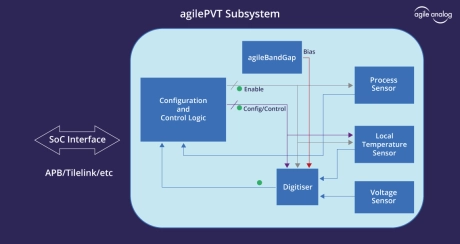

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

-

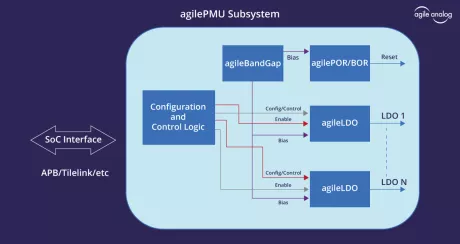

Power Management Subsystem

- The agilePMU Subsystem is an efficient and highly integrated Power Management Unit for SoCs/ASICs.

- Featuring a Power-On-Reset (POR), multiple Low Drop-Out (LDO) regulators, and an associated reference generator.

- The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities.

-

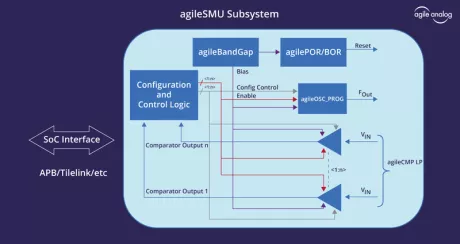

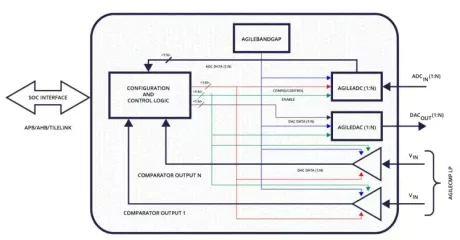

Sensor Interface Subsystem

- The agileSensorIF Subsystem is an efficient and highly integrated sensor interface for SoCs/ASICs.

- Featuring multiple Analog-to-Digital Converters (agileADC), Digital-to-Analog Converters (agileDAC), low-power programmable analog comparators (agileCMP_LP), and an associated reference generator (agileREF).

- The agileSensorIF Subsystem enables easy interaction with the analog world.

-

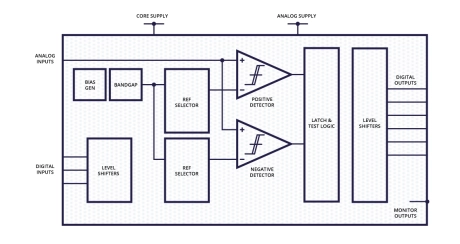

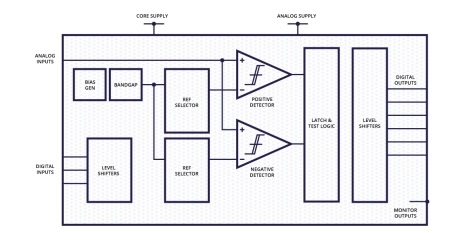

Voltage Glitch Detector

- The agileVGLITCH voltage monitor provides security and protection against voltage side-channel attacks (SCA) and tampering such as supply voltage changes/glitches and power supply manipulation.

- The sensor provides digital outputs to warn (secure) processors of intrusion attempts, thus enabling a holistic approach to hardware security.

-

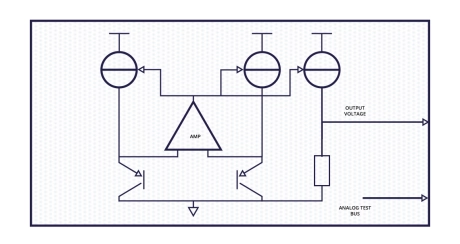

Temperature Sensor (Analog Output)

- The agileTSENSE_A GP Temperature Sensor is a traditional ΔVBE temperature sensor that amplifies the difference between two VBE voltages, and converts the result to a single-ended signal.

- This temperature sensor can be used with the agileADC in order to provide a digital output with an overall relative accuracy of +/-0.25°C.

- On modern SoCs, thermal management is critical for detection of security attacks and optimization of power, performance and area.