32-bit RISC-V CPU IP

Filter

Compare

50

IP

from

8

vendors

(1

-

10)

-

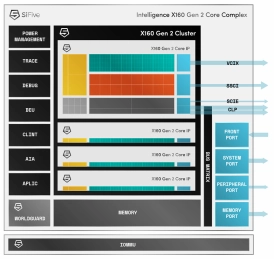

Multi-core capable 32-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X160 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 32-bit version, X100 series IP can be optimized for power efficiency and severely area-constrained applications.

-

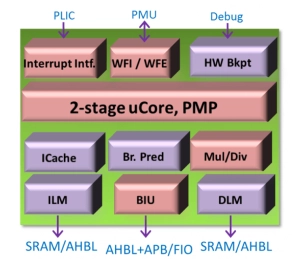

Ultra Compact 32-bit RISC-V CPU Core

- AndesCore™ N22 is a 32-bit 2-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications that require low energy consumption and small area.

- It is compliant to RISC-V technology with several efficient performance features, including simple dynamic branch prediction, instruction cache, and local memories.

-

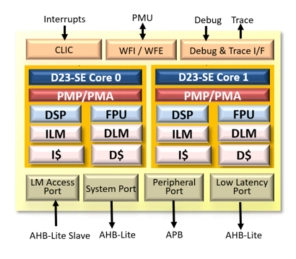

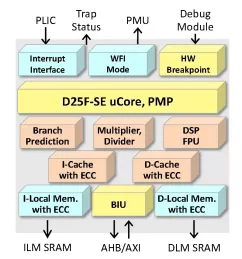

ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core

- The AndesCore™ D23-SE is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V IMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), CMO (cache management operations) as well as Zce (code size reduction), plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

32-bit CPU IP core - ISO 26262 Automotive Functional Safety Compliant

- 32-bit CPU IP core that supports ISO 26262 ASIL B level functional safety for automotive applications

-

ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- 32-bit RISC-V embedded CPU with balanced 3-stage pipeline

- DSP implementation to extend the RISC-V baseline (RMX-100D)

- 2 KB to 64 KB instruction L1 cache

- Up to 2MB instruction and data closely coupled memory (CCM)

-

ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- High-speed, 32-bit, dual-issue, 10-stage pipeline

- Multicore support for up to 16 CPUs and up to 16 user hardware accelerators per processor cluster

-

ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- 32-bit RISC-V embedded CPU with a 5-stage pipeline

- DSP implementation to extend the RISC-V baseline (RMX-500D)

- 2 KB to 64 KB instruction & data L1 caches

-

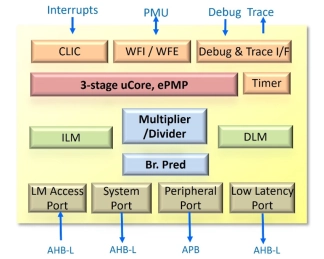

Compact and Performance Efficiency 32-bit RISC-V Core

- The N225 is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V IMAC it supports the recently ratified ISA extensions such as B (bit manipulation) and Zce (code size reduction).

-

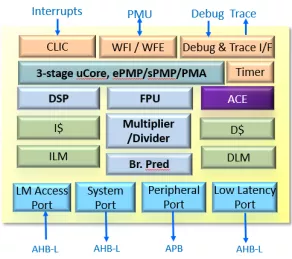

Compact, Secure and Performance Efficiency 32-bit RISC-V Core

- AndesCore™ D23 is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5/V5e architecture for embedded applications with small gate count, and some dual-issue ability.

- In addition to commonly used RISC-V I/EMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), and CMO (cache management operations) as well as Zce draft (code size reduction).

-

RISC-V CPU IP With ISO 26262 Automotive Functional Safety Compliant

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- Floating point extensions

- Bit-manipulation extensions