ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core

The AndesCore™ D23-SE is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with …

Overview

The AndesCore™ D23-SE is a 32-bit 3-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications with small gate count, and some dual-issue ability. In addition to commonly used RISC-V IMAC, single/double precision FPU and DSP extensions, it supports the recently ratified ISA extensions such as B (bit manipulation), K (scalar cryptography), CMO (cache management operations) as well as Zce (code size reduction), plus Andes Custom Extension™ (ACE) for user-defined instructions. D23-SE supports split-mode that 2 cores could run independently when split-lock is configured. Safety features include dual-core lockstep (DCLS) that is a real-time diagnostic using an additional processor and a comparator to enhance the diagnostic coverage; ECC for memory soft error protection; bus protection to protect bus transaction; core trap status bus interface provides real time information of trap status from core. Approved based on the functional safety assignments of a Safety Element Out-of-Context (SEooC), which includes the ISO 26262 compliant development process and the qualitative as well as quantitative approaches with respect to hardware safety analysis, D23-SE is certified to be ASIL-B/D and used in highest safety-related applications.

Functional Safety

- AndesCore™ D23-SE processor core certified by parts 2, 4, 5, 7, 8 and 9 of the standards, meeting the architectural metrics and random hardware fault metrics requirements for ASIL B/D

- D23-SE supports split-mode that 2 cores could run independently when split-lock is configured. ECC for memory soft error protection; bus protection to protect bus transaction; core trap status bus interface provides real time information of trap status from core.

- Safety Mechanism: Split/Lock (ASIL-B/D); Single Core (ASIL-B)

- Three product name: D23-SE-DCLS; D23-SE-DCLS-LOCK; D23-SE-SC

Key features

- AndeStar™ V5 ISA, including:

- RV32 I,M,A,C,F,D,B,P,K,CMO, and Zce

- Andes extensions for performance and functionality enhancements

- 3-stage pipeline optimized for gate count and efficiency

- 16/32-bit mixable instructions for code density

- Instruction and data caches to speed up accessing embedded or external flash memory

- Branch predication to speed up control code

- Enhanced and Supervisor-mode Physical Memory Protection (ePMP and sPMP) to enhance core security

- Core-Local Interrupt Controller (CLIC) for fast response, interrupt prioritization and pre-emption and Platform-Level Interrupt Controller (PLIC) for a wide range of cores and system event scenarios

- Patented CoDense™ technology to compress program code on top of the 16-bit extension

- Instruction Trace Interface supports RISC-V Processor Trace v2.0

- Fast interrupt response with shadow registers

- Separately licensable Andes Custom Extension™ (ACE) for customized acceleration

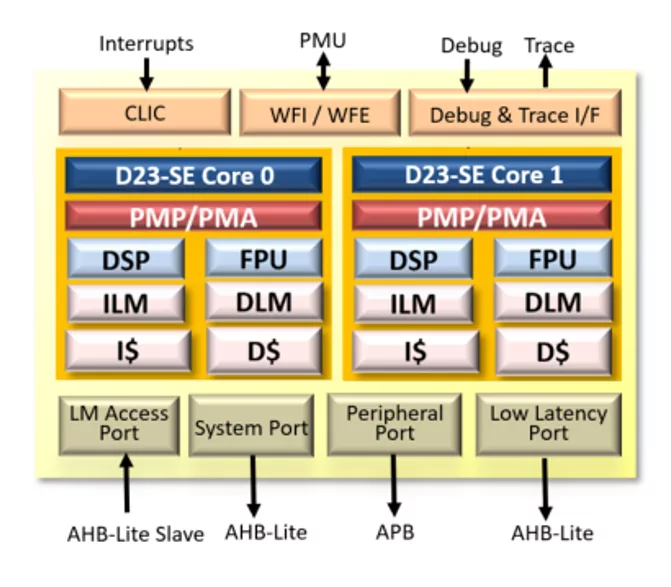

Block Diagram

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core?

ISO26262 ASIL-B/D Compliant 32-bit RISC-V Core is a CPU IP core from Andes Technology Corp. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.