Ethernet PHY IP

Welcome to the ultimate Ethernet PHY IP hub! Explore our vast directory of Ethernet PHY IP

The Ethernet PHY IP cores encode data frames for transmission and decode received frames with a specific modulation speed of operation, transmission media type and supported link length.

All offers in

Ethernet PHY IP

Filter

Compare

65

Ethernet PHY IP

from

14

vendors

(1

-

10)

-

OPEN Alliance TC14 10BASE-T1S Topology Discovery IP

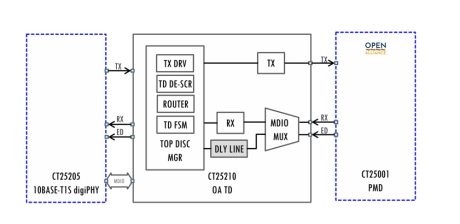

- The CT25210 Topology Discovery (TD) IP coordinates all operations required to perform 10BASE-T1S topology discovery measurements. It integrates several functional blocks, each responsible for a specific phase of configuration, training, measurement, and signal handling within the discovery process.

- At the top level, the TD Manager supervises the measurement flow and configuration setup. Within this block, the TD Mode Manager manages the receive-only operating mode and distributes the necessary clock signals to other TD modules.

-

Ethernet PHY IP

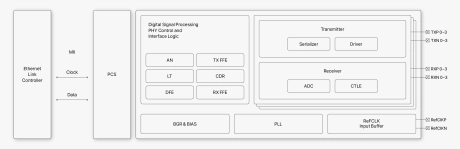

- Compliant to 802.3 Ethernet specification - 200GBASE-KR4, 200GBASE-CR4, 100GBASE-KR4, 100GBASE-CR4, 100GBASE-KR2, 100GBASE-CR2, 50GBASE-KR, 50GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 25GBASE-KR, 25GBASE-CR, 10GBASE-KR, 10GBASE-CR

- Data rate supported - Ethernet: NRZ 3.125 - 26.5625Gb/s, PAM4 53.125Gb/s

- DSP-based architecture using high-performance ADC/DAC for RX/TX

-

Ultra-Low-Latency 10GE PHY+MAC

- Ultra-low-latency round-trip (fiber-to-fiber or gate-to-gate) for 10 Gigabit Ethernet, first-bit to first-bit

- Reconciliation sub-layer implementation compliant with IEEE802.3

- Local fault and remote fault detection and handling

- Frame Check Sequence (FCS) insertion and verification at line rate

-

-

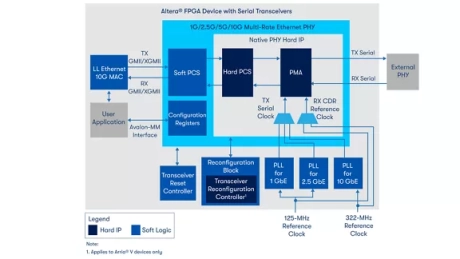

Multi-Rate Ethernet PHY FPGA IP

- The Multi-Rate Ethernet PHY FPGA IP core can dynamically support multiple data rates without any design regeneration or device reconfiguration

- This IP allows the creation of a 1G to 10G configuration that allows dynamic reconfiguration across all Ethernet rates from 10M, 100M, 1G, 2.5G, 5G, and 10G.

-

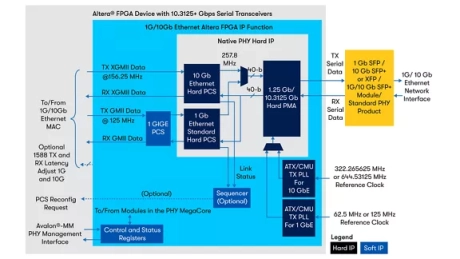

1G/10Gb Ethernet PHY Intel® FPGA IP

- The 1G/10G Ethernet PHY Intel® FPGA Intellectual Property (IP) core supports functionality of both the standard physical coding sublayer (PCS) and the higher data rate 10G PCS with an appropriate physical medium attachment (PMA)

- The Standard PCS implements the 1GbE protocol as defined in Clause 36 of the IEEE 802.3 2005 Standard and also supports auto-negotiation as defined in Clause 37 of the IEEE 802.3 2005 Standard

- The 10G PCS implements the 10G Ethernet protocol as defined in the IEEE 802.3 2005 standard.

-

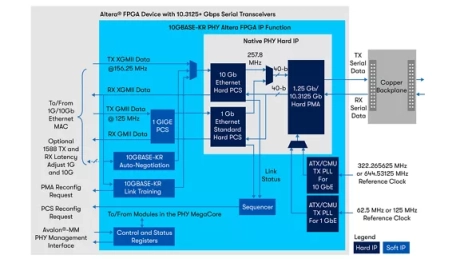

Backplane Ethernet 10GBASE-KR PHY Intel® FPGA IP Core

- The Backplane Ethernet 10GBASE-KR PHY Intel® FPGA Intellectual Property (IP) core is a transceiver PHY that allows you to instantiate both the hard standard physical coding sublayer (PCS) and the higher performance hard 10G PCS, and hard physical medium attachment (PMA) for a single Backplane Ethernet channel

- It implements the functionality described in the IEEE 802.3ap-2007 standard

- Because each instance of the 10GBASE-KR PHY IP core supports a single channel, you can create multichannel designs by instantiating more than one instance of the core.

-

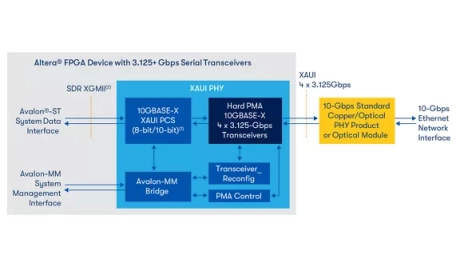

XAUI PHY Intel® FPGA IP

- The XAUI PHY Intel® FPGA IP core allows you to easily build systems with a very high throughput 10G Ethernet connection

- This XAUI PHY along with a 10GbE media access control (MAC) IP core enables an Intel® FPGA to interface to a 10GbE network through a variety of external devices, including a 10GbE PHY device or optical transceiver module.

-

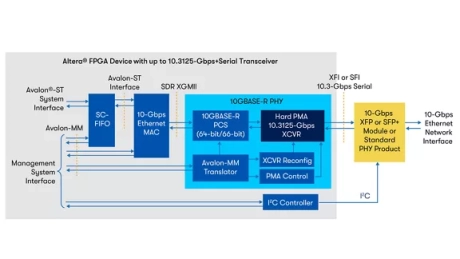

10GBASE-R PHY Intel® FPGA IP

- The 10GBASE-R PHY Intel® FPGA Intellectual Property (IP) core allows connectivity directly with any XFP or SFP+ optical module or with any external device with XFI and SFI interfaces.

-