Bridge

A integrated hardware and software solution that includes a TSN-capable Ethernet switch, a DMA engine, an IEEE 802.1 AS Time Sync…

Overview

A complete integrated hardware and software solution that includes a TSN-capable Ethernet switch, a DMA engine, an IEEE 802.1 AS Time Synchronization system, and a Root of Trust security module.

A bridge is a network device that connects multiple TSN-enabled network segments, including End Stations, Gateways, Zonal Controllers, Computers, and other Bridges, while ensuring deterministic, low-latency communication through the implementation of TSN features. Like a traditional Ethernet switch, the bridge forwards frames between ports based on MAC addresses, but it also incorporates TSN features for scheduling, filtering, and traffic management to deliver reliable, time-critical communication.

Comcores offers a versatile portfolio of Bridge IPs, tailored to support varying performance levels and a wide range of TSN features. These IPs are well-suited for demanding applications in automotive, industrial, avionics, and defence industries.

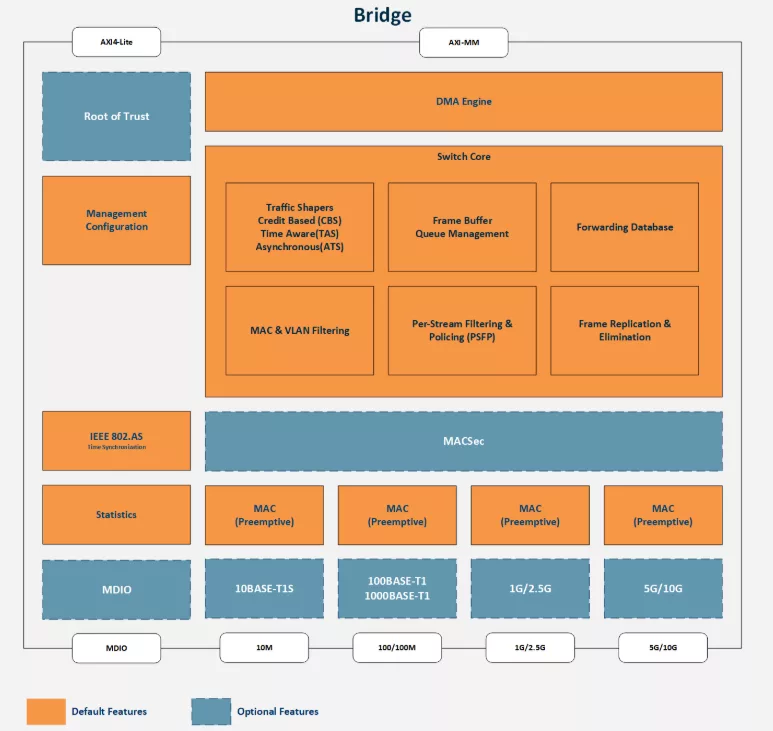

The Bridge IP from Comcores is a complete solution that integrates both hardware and software components. It includes a TSN-capable Ethernet switch, a DMA engine, an IEEE 802.1 AS Time Synchronization system, and a Root of Trust security module.

The solution connects easily to embedded processor systems through an AXI Memory-Mapped interface for Ethernet frame exchange, and an AXI4-Lite interface for management and configuration tasks.

Technical Specifications

The Bridge IP supports up to thirty-two physical Ethernet ports operating at 10M, 100M, 1G or 2.5G, and two additional ports operating at 10 Gbps. These ports interface with Ethernet PHY devices through standard interfaces such as MII, RMII, GMII, RGMII, SGMII, USGMII, USXGMII, or XFI. The solution supports Single Pair Ethernet (SPE) standards like 10BASE-T1S, 10BASE-T1L, 100/1000BASE-T1, and 2.5G/5G/10GBASE-T1, as well as traditional electrical and optical Ethernet standards. A built-in MDIO controller enables management and configuration of the connected PHY devices.

For time-sensitive applications, the Bridge IP incorporates several TSN mechanisms including Time Aware Shaping (TAS), Credit Based Shaping (CBS), and Asynchronous Traffic Shaping (ATS) to ensure deterministic and low-latency data delivery.

The Bridge IP also supports preemptive Media Access Control (MAC) functionality, which allows higher-priority frames to interrupt the transmission of lower-priority traffic, minimizing delay for time-critical communications.

Reliability features include support for frame replication and elimination as defined by IEEE 802.1CB. This allows the system to transmit critical data over redundant paths, ensuring uninterrupted communication even in the event of a single network fault.

The Bridge IP implements per-stream filtering and policing based on IEEE 802.1Qci, guaranteeing that each data stream behaves as expected with respect to rate, timing, and integrity.

VLAN management and packet forwarding adhere to IEEE 802.1Q, supporting up to eight unique traffic classes for Quality of Service (QoS) differentiation. Both cut-through and store & forward operation is supported by the Bridge IP.

An optional MACsec engine provides Layer 2 Ethernet security, enabling port authentication, encryption, and integrity checking in compliance with IEEE 802.1AE. This feature allows configurat ion of multiple Security Entities (SecYs) per port, supporting different traffic types securely.

A DMA engine is included to transfer Ethernet frames between the memory of embedded processor system and the Bridge IP with minimal interaction required from the CPU.

The Bridge IP also supports precise timing and synchronization using IEEE 802.3AS and its amendment IEEE 802.1ASds, which is essential for half-duplex operation. A built-in wall clock and phase adjustment mechanism reduce CPU load by minimizing the need for software-based synchronization adjustments.

Security is enforced through the integrated Root of Trust module, which ensures a secure boot process by validating software before execution. This module also handles secure storage, key generation, and cryptographic random number generation, supporting secure communication features such as MACsec. It is designed with tamper resistance and restricts access to sensitive operations during runtime.

Block Diagram

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Bridge?

Bridge is a Protocol Bridge IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.