Ethernet PHY IP

The 56G/64G PAM4 SERDES hard macro IP delivers a high-performance, low-power solution for high-speed serial interfaces.

Overview

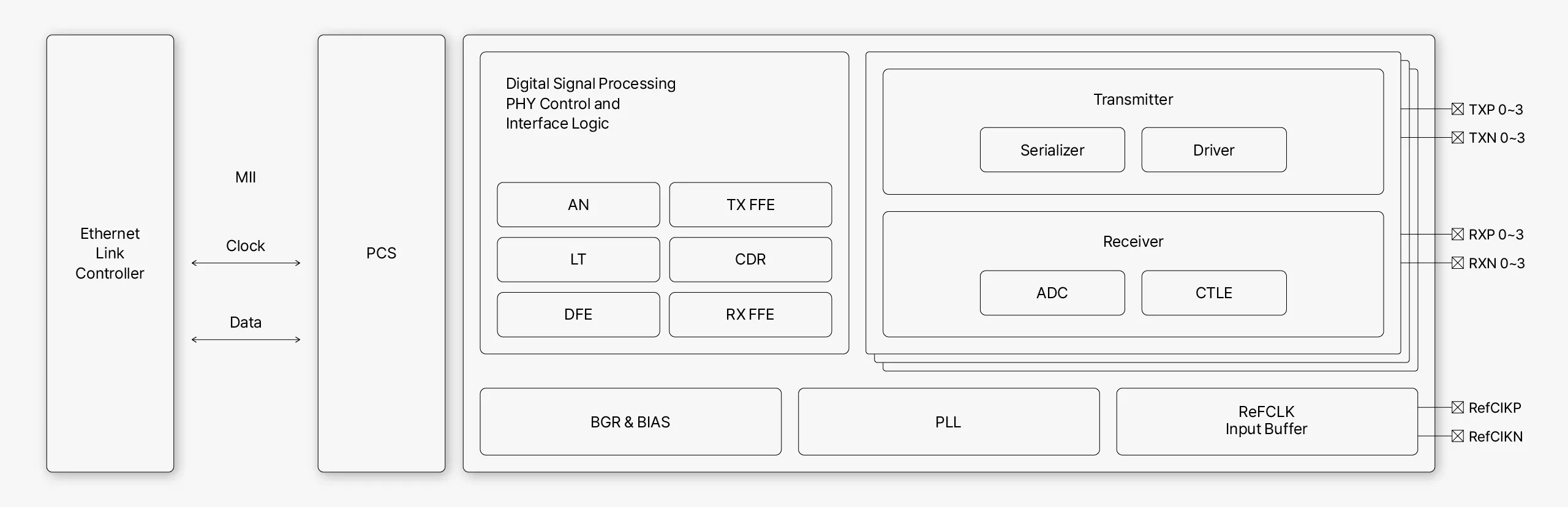

The 56G/64G PAM4 SERDES hard macro IP delivers a high-performance, low-power solution for high-speed serial interfaces. Supporting data rates up to 64Gbps per lane, it is optimized for next-generation Ethernet, PCIe, and custom high-speed links in AI accelerators, networking switches, and chiplet-based SoCs.With support for PAM4 and NRZ signaling, advanced equalization, and scalable lane architecture, this IP ensures robust signal integrity across long-reach and high-loss channels.

Key features

- Compliant to 802.3 Ethernet specification - 200GBASE-KR4, 200GBASE-CR4, 100GBASE-KR4, 100GBASE-CR4, 100GBASE-KR2, 100GBASE-CR2, 50GBASE-KR, 50GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 25GBASE-KR, 25GBASE-CR, 10GBASE-KR, 10GBASE-CR

- Data rate supported - Ethernet: NRZ 3.125 - 26.5625Gb/s, PAM4 53.125Gb/s

- DSP-based architecture using high-performance ADC/DAC for RX/TX

- Lane configurations: X1, X2 or X4

- PCS in soft-macro and PMA in hard-macro

- Reed / Solomon Forward Error Correction(RS FEC)

- MCU and firmware-driven Link Training(LT)/Auto Negotiation(AN) delivers flexible functionality and tuning.

- RX eye-opening monitor

- Loopback feature capable of generating and checking PRBS patterns

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is Ethernet PHY IP?

Ethernet PHY IP is a Single-Protocol PHY IP core from Qualitas Semiconductor listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.