Ethernet MAC IP

Welcome to the ultimate Ethernet MAC IP hub! Explore our vast directory of Ethernet MAC IP cores

The Ethernet MAC IP cores enable the host to communicate data using the Ethernet protocol (IEEE 802.3) at 10 or 100 Mbps speeds. These IP cores are composed of three main layers: the Media Access Controller (MAC), the MAC Transaction Layer (MTL), and the MAC DMA Controller (MDC).

All offers in

Ethernet MAC IP

Filter

Compare

286

Ethernet MAC IP

from

59

vendors

(1

-

10)

-

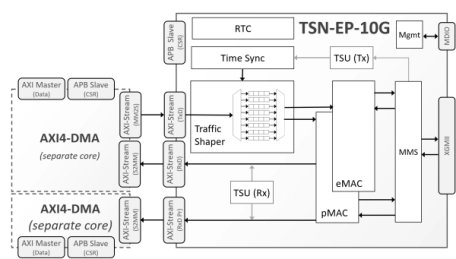

TSN Ethernet Endpoint Controller 10Gbps

- The TSN-EP-10G implements a configurable controller meant to ease the implementation of endpoints for networks complying with the Time Sensitive Networking (TSN) standards

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

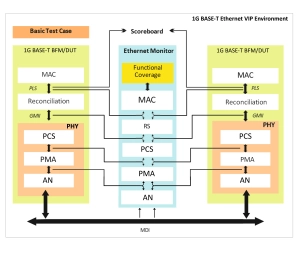

1G BASE-T Ethernet Verification IP

- The 1G BASE-T Ethernet Verification IP provides deliverables an effective & efficient way to verify the components interfacing with the Ethernet interface of an IP or SoC.

- The 1G Ethernet VIP is fully compliant with the IEEE standard 802.3 specification.

- This VIP is lightweight with easy plug -and- play interface so that there is no hit on the design cycle time.

-

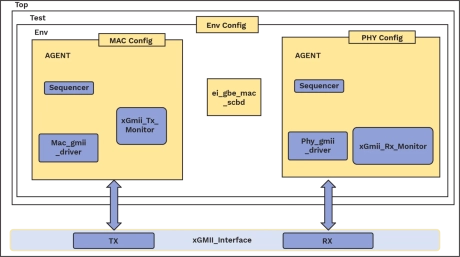

Simulation VIP for Ethernet UEC

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Callbacks access at multiple TX and RX queue points for scoreboarding, data manipulation, and error injection

- Transaction Tracker: Configurable tracking of all the transactions on the channels

-

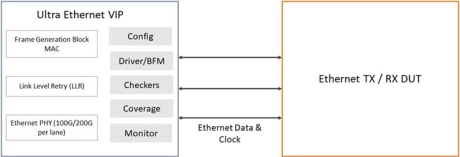

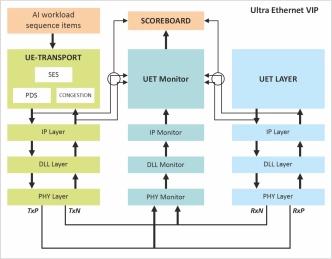

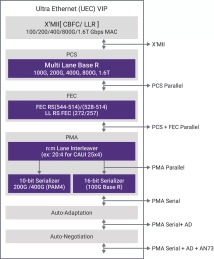

Ultra Ethernet Verification IP

- The Ultra Ethernet (UE) Verification IP provides an effective & efficient way to verify the components interfacing with Ethernet interface of an IP or SoC.

- The UE VIP is compliant with IEEE standard 802.3-2018 & UE Specifications V1.0.

- This VIP is light weight with easy plug-and-play interface so that there is no hit on the design cycle time.

-

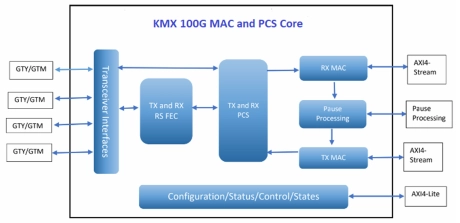

100G MAC and PCS core

- KMX 100G MAC and PCS core, which consists of media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core implements RS FEC as defined in IEEE 802.3bj Clause 91 with independent bit error detection and bit error correction.

-

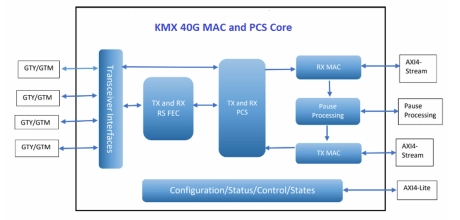

40G MAC and PCS core

- KMX 40G MAC and PCS core, which including media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core supports RS FEC as defined in Clause 74 IEEE 802.3 with independent error bit detection and error bit correction.

-

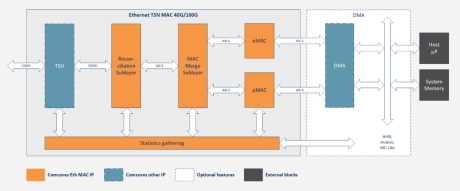

Ethernet TSN MAC 40G/100G

- Silicon agnostic Ethernet TSN MAC IP with speeds of 40G and 100G, based IEEE 802.3 Ethernet Layer 2 solution with support for key TSN features

-

Verification IP for Ultra Ethernet (UEC)

- Native SystemVerilog/UVM

- Source code test suite including UNH-IOL (optional)

- Runs natively on major simulators

- Built-in protocol checks

- Verification plan and coverage

-

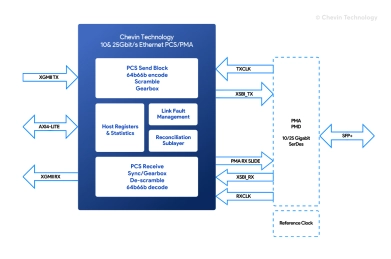

10G/25G/40G/100Gbit/s Ethernet MAC/PCS

- 10/25/40/100 Gbit Ethernet Connectivity in Intel and AMD/Xilinx FPGA

- Designed to IEEE 802.3by specification

- Low latency, TX 11ns, RX 8ns (Modes: cut-through/store-and-forward)

- Integrated FCS(CRC32) checker and generator

-

100G Ethernet Verification IP

- The 100G Ethernet Verification IP (VIP) offers a robust and high-performance solution for validating the critical MAC-to-PCS datapath in 100 Gigabit Ethernet systems.

- Designed to ensure protocol compliance, the VIP facilitates the generation, transmission, reception, and monitoring of various Ethernet MAC frame types, all while adhering to IEEE 802.3ba and related standards.

- Whether you are working on IP, subsystem, or SoC-level verification, this VIP is your go-to solution for comprehensive Ethernet testing.