Analog IP for TSMC

Welcome to the ultimate

Analog IP

for

TSMC

hub! Explore our vast directory of

Analog IP

for

TSMC

All offers in

Analog IP

for

TSMC

Filter

Compare

105

Analog IP

for

TSMC

from

9

vendors

(1

-

10)

Filter:

- 3nm

-

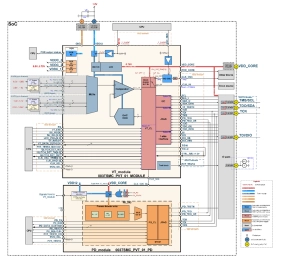

Process/Voltage/Temperature Sensor with Self-calibration (Supply voltage 1.2V) - TSMC 3nm N3P

- 003TSMC_PVT_01 IP library is a unique solution intended to continuously monitor IC status at several on-die locations.

- It is able to detect manufacturing process deviation, perform voltage, current and die temperature measurement.

-

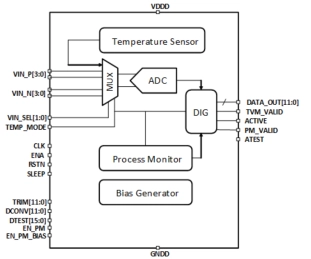

Ultra-Low-Power Process, Voltage, and Temperature Monitor in 3nm

- The ODT-PVT-ULP-001C-3nm is an ultra-low power temperature, voltage and process monitor designed in a 3nm CMOS process.

- This IP operates over the entire temperature range of -40°C to 150°C.

- The temperature monitor achieves ±4C temperature accuracy without trim and ±1C temperature accuracy after a single room temperature trim.

- The voltage monitor supports four differential or singleended inputs with a voltage range up to ±0.75V.

-

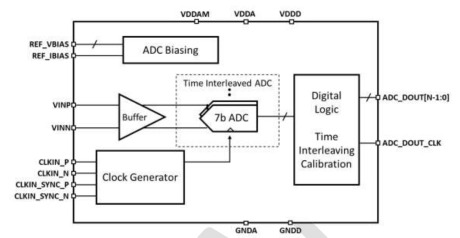

Ultra-High-Speed Time-Interleaved 7-bit 64GSPS ADC on 3nm

- The ODT-ADS-7B64G-3 is an ultra-high-bandwidth time-interleaved ADC designed in a 3nm CMOS process.

- This 7-bit, 64GSPS ADC supports ac-coupled input signals up to Nyquist and features a full-scale range of 0.45Vpp differential, excellent dynamic performance, and low noise operation.

-

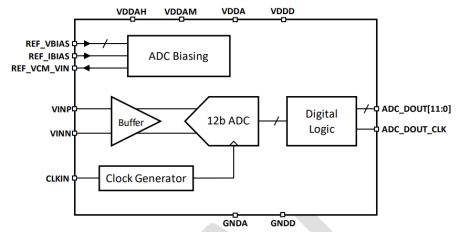

12bit, 400 MSPS ADC Ultra Low Power

- Ultra high-performance low-power ADC

- Integrated input buffer

- 12-bit ADC resolution

- Sampling rate of 500MSPS

- Fully differential operation

- 0.8Vpp differential input signal range

-

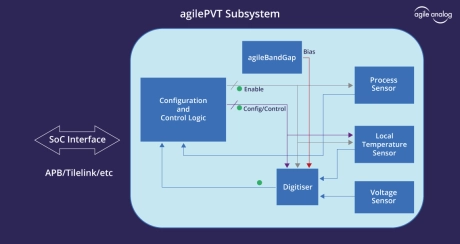

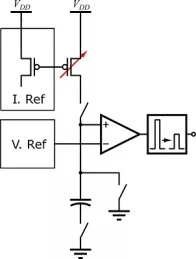

PVT Sensor Subsystem

- Start-up time: Typ 20us

- Current consumption: Max 25uA

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

-

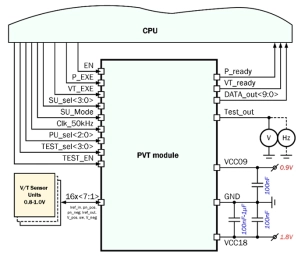

Process/Voltage/Temperature Sensor (Supply voltage 1.8V/0.9V)

- TSMC 28nm 28HPC CMOS

- High accuracy temperature and voltage measurements

- Process detector for all-voltage threshold MOS transistors

- Up to 16 remote temperature/voltage sensors

-

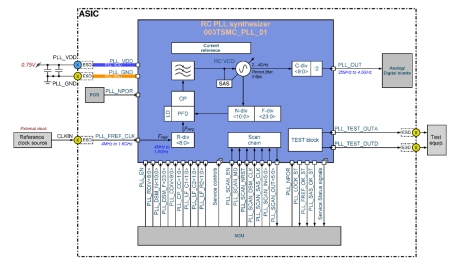

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.

-

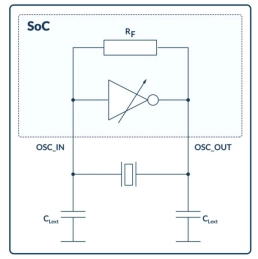

Crystal Oscillators

- The crystal oscillator macros are available in a wide range of industry-standard quartz crystals and MEMS resonators operating in the fundamental mode in the 32 kHz to 80 MHz range.

- These oscillators, which are both power and area efficient, have a programmable transconductance to allow users to find the optimal balance between jitter and power consumption.

-

Free running oscillators

- Compact and low power

- No external components

- Baseline CMOS logic process masks only

- Excellent frequency precision over PVT after trimming

-

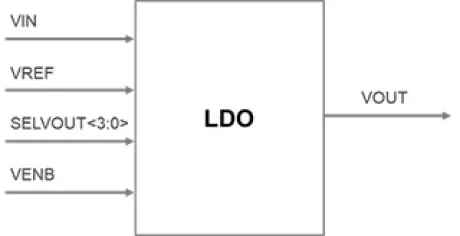

LDO Voltage Regulator, Adjustable 0.45 V to 0.9 V Output, 30 mA, TSMC N3P

- The LDO IP is a 1.2V low-quiescent-current adjustable output voltage Low-Drop-Out (LDO) Linear Regulator implemented in the TSMC 3nm N3P CMOS process technology.

- Its low sleep current, 30 mA maximum current, output voltage adjustability and precision make it especially suitable for use as an integrated voltage regulation source for subsystems implemented in analog, digital, mixed-signal and RF ASICs and SoCs.