Power Management IP for Silterra

Welcome to the ultimate

Power Management IP

for

Silterra

hub! Explore our vast directory of

Power Management IP

for

Silterra

All offers in

Power Management IP

for

Silterra

Filter

Compare

12

Power Management IP

for

Silterra

from

2

vendors

(1

-

10)

-

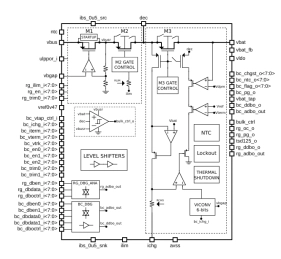

Linear Li-Ion Battery Charger - Programmable charging current up to 1.1A Fast Charge - SilTerra 0.18um

- This USB/AC Li-Ion battery charger is targeted for portable applications.

- The charging current can be adjusted from 60mA up to 1.1A through an external resistor or by digital control.

- The current provided to the system can also be adjusted up to 1.8A through the same procedure.

-

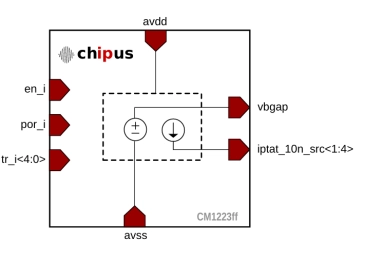

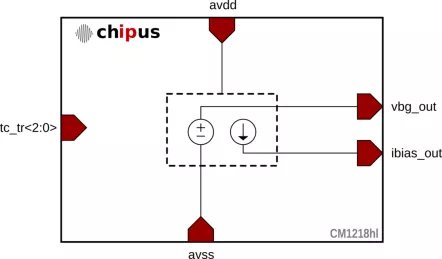

ULP Bandgap Voltage Reference - 210nA consumption, 40ppm/ºC - Silterra 0.18um

- This macro-cell is an ultra-low-power bandgap voltage reference (1.23V) with low temperature coefficient (>40ppm/ºC) consuming 210nA.

- A 5-bit digital bus allows TC adjust against process variations. It provides a built-in 10nA PTAT current reference with 4 outputs.

-

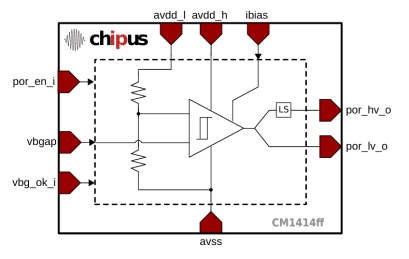

Power-On Reset - Threshold (1.6V1.8V), Low Current (1.5µA) - Silterra 0.18 um

- This macro-cell is a low consumption Power-On Reset (POR) core designed for SilTerra 0.18μm CL180GH5 5V CMOS technology.

- The threshold sensing voltage ranges from 1.6V to 1.8V (default is 1.65V). A hysteresis of 100mV is added to avoid false reset glitches in noisy supplies.

-

Bandgap Voltage Reference - Low Integrated Noise (57.2µVrms) -TSMC 40nm

- Vref=0.57V ±3.8% (without trimming)

- 17.2uA current consumption in active mode

- Supply voltage: 1.0–1.32V

- Output noise: 57.2uVrms (integrated up to 20MHz)

-

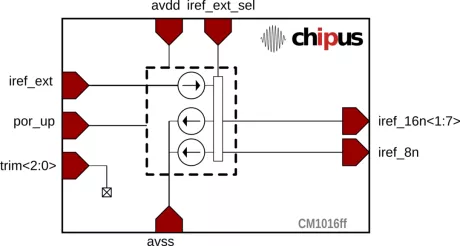

16nA Resistive Current Bias Low Voltage (1.0V), Low Power (360nW @ 1.2V)

- This macro-cell is a low power general purpose current bias generator core designed for SilTerra 0.18µm CL180G CMOS technology.

- The circuit generates 7 × NMOS 16nA current branches and 1 × NMOS 8nA branch. The current bias is temperature compensated using the PTAT thermal coefficient (TC) of an integrated resistor.

-

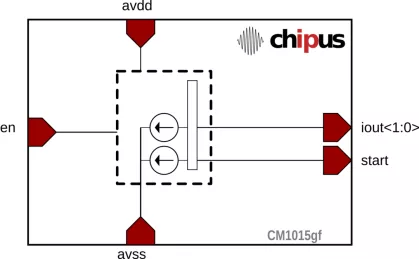

17nA Current Bias with Enable Low Voltage (1.0V), Ultra Low Power (90nW @ 1.8V)

- This macro-cell is a low power general purpose current bias generator core designed for TowerJazz 0.18µm TS18SL CMOS technology.

- The circuit generates 2 × NMOS 17nA current branches. The current bias is temperature compensated.

-

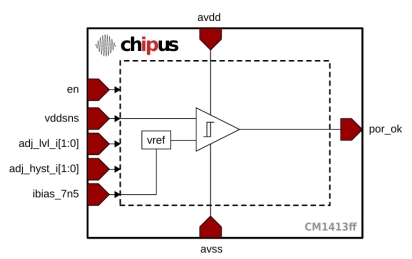

Power-On Reset - Flexible Threshold (1-1.3V), Ultra Low Current (100nA) - Silterra 0.18 um

- This macro-cell is an ultra low consumption Power-On Reset (POR) core designed for SilTerra 0.18μm CL180G CMOS technology.

- The threshold sensing voltage can be configured from 1V to 1.3V (default is 1.15V).

- A hysteresis of 120mV is added to avoid false reset glitches in noisy supplies. This value can be digitally configured from 70mV to 200mV.

-

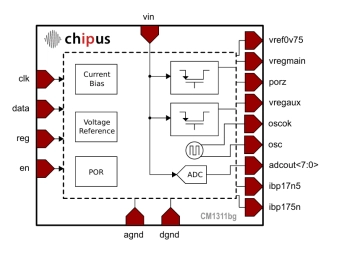

Ultra Low Power PMU - Ultra Low Voltage (Vin > 1.2V), Ultra Low Power (6µW) - LFoundry 0.15 um

- This macro-cell is an ultra low consumption Power Management Unit (PMU) core designed for LFoundry 0.15µm LF150 CMOS technology STD (Standard) and LP (Low Power) process.

- The circuit has 2 LDO voltage regulators, internal voltage and current references, built-in power-on-reset and oscillator, and an 8-bit low power and low frequency ADC for general purpose voltage monitoring.

-

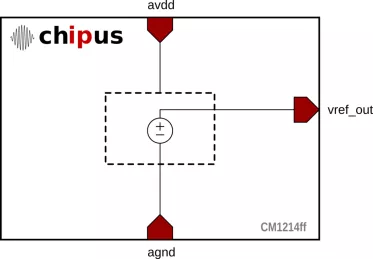

ULP Bandgap Reference - Ultra Low Current (150nA) Silterra 0.18 um

- This macro-cell is an ultra low power voltage reference generator core designed for SilTerra 0.18µm CL180G CMOS technology.

- The core is ideal as a general purpose reference voltage in applications where power consumption is critical.

- The circuit generates an unbuffered 1180mV, temperature compensated bandgap voltage reference (47ppm/ C).

-

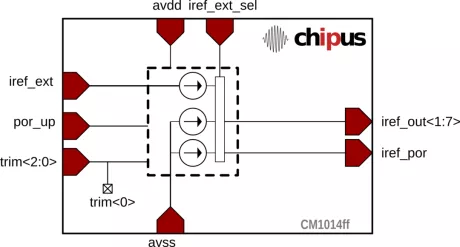

17nA Current Bias with Trimming Ultra Low Voltage (0.9V), Ultra Low Power (70nW)

- This macro-cell is an ultra low power general purpose current bias generator core designed for SilTerra 0.18µm CL180G CMOS technology.

- The circuit generates 7 × NMOS 15.5nA current branches and 1 × NMOS 7.75nA branch. The current bias is temperature compensated.