Pipelined Floating Point FFT IP Core

The Pipelined FFT IP Core provides efficient continuous data FFT calculations at the rate of one point per clock cycle.

Overview

The Pipelined FFT IP Core provides efficient continuous data FFT calculations at the rate of one point per clock cycle.

Used in both FPGA and ASIC devices, and excellent for applications where low memory usage is desired. Can result in the least ASIC area usage because of low memory requirement for medium to long FFT lengths.

We provide cores for Xilinx and Altera FPGAs (using inferred block RAM and their math IP cores for floating point applications), as well as provide ASIC-targeted or FPGA-to-ASIC roadmap cores (using SRAM wrappers and our own fixed or floating point math cores).

Key features

- Any radix-2 length

- Variable length option for runtime per-transform length select

- Clock rates to 400MHz in Virtex-5

- Fixed or floating point math

- Efficient memory usage, useful for ASIC applications

- Continuous data processing

- Optimized butterfly structure in each rank, consumes and produces one point per clock cycle

- Decimation-in-Frequency (DIF) has normal order input, out of order output

- Decimation-in-Time (DIT) has out of order input, normal order output.

- Optional input or output buffer, for completely normal order I/O

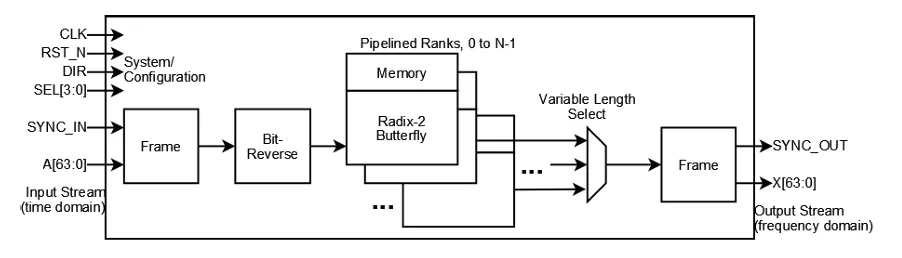

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is Pipelined Floating Point FFT IP Core?

Pipelined Floating Point FFT IP Core is a Filters Transforms IP core from Dillon Engineering, Inc. listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.