General-purpose FFT core

The FFT is factored into Radix-4 Butterfly operations.

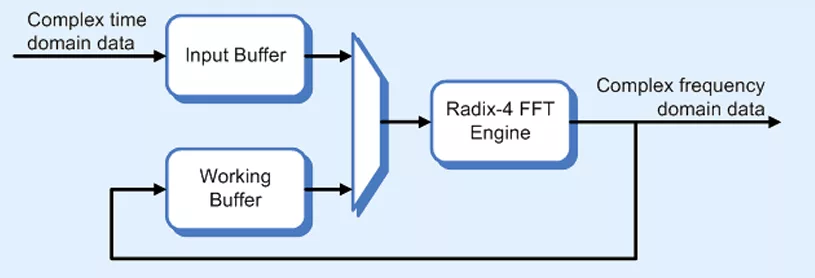

Overview

The FFT is factored into Radix-4 Butterfly operations. When an odd power of two is required, a small radix-2 “follower” stage performs the final iteration. The radix-2 stage does not require a full complex rotator so its cost is minimal.

The Radix-4 Engine fetches one complex word of data each clock cycle. Four interleaved data words are collected then applied to the t0-t3 inputs. On successive clock cycles the engine calculates the four frequency domain outputs f0-f3. These are then stored back into the Working Buffer.

During the final iteration, the engine produces frequency domain outputs on successive clocks. These arrive in scrambled (digit-reversed) order.

A final pass through the data produces outputs in sorted order.

Key features

- Typical applications include COFDM modems for 802.11a, 802.16 and DVB-T.

- Synthesis controls allow FFT sizes = 2n with support for multiple run-time sizes such as 2k/4k/8k modes for DVB-T/H.

- Performs forward or inverse FFT.

- Generates cyclic prefix as required by most COFDM standards.

- I/O structures support both Time Domain (real-time) and Frequency Domain (burst mode) interfaces.

- Synthesis control of signal precision (variable width).

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Our expertise is primarily in the gate- and power-efficient implementation of physical-layer (PHY) functions such as: modulation, demodulation, equalisation and channel coding but our experience encompasses all of the major elements of a modern baseband 'core' including the medium access control (MAC), voiceband DSP, mixed-signal interfaces, and embedded Cpu and software.

Our services are provided on a turnkey basis or as part of a support package attached to our licenced IP or tool products.

Commsonic's customers are typically semiconductor vendors and manufacturers of communications equipment that require leading-edge, Standards-based or proprietary PHY solutions but lack the internal resources or skills necessary to deliver projects against aggressive deadlines.

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is General-purpose FFT core?

General-purpose FFT core is a Filters Transforms IP core from Commsonic Ltd listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.