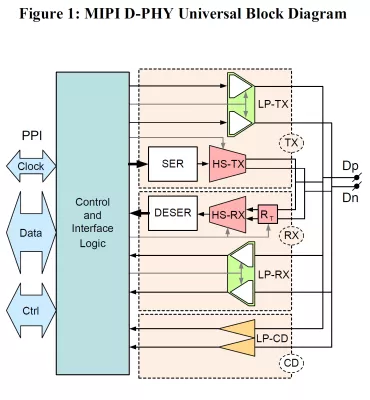

The MXL-DPHY-UNIVERSAL-T-40LP is a high-frequency low-power, low-cost, source-synchronous, Physical Layer compliant with the MIPI Alliance Standard for D-PHY.

The IP can be configured as a MIPI master or slave and consists of 5 lanes: 1 Clock lane and 4 data lanes.

The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed Data traffic while low power functions are mostly used for control.

MIPI D-PHY Universal IP in TSMC 40LP for Automotive

Overview

Key Features

- Consists of 1 Clock lane and 4 Data lanes

- Complies with MIPI Standard 1.1 for D-PHY

- Supports both high speed and low-power modes

- 80 Mbps to 1.0/1.5 Gbps data rate in high speed mode

- 10 Mbps data rate in low-power mode

- High Speed Serializer and De-Serializer included

- Low Power dissipation

Benefits

- Supports both MIPI CSI-2 and MIPI DSI, as a transmitter and receiver

- Silicon proven in TSMC 40LP

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

TSMC, 40nm LP

Maturity

Silicon Proven

Availability

Now

TSMC

Silicon Proven:

40nm

LP

Related IPs

- ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm

- Universal Multi-port Memory Controller for RLDRAM2/3, DDR5/4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- SD 4.0 UHS-II PHY in TSMC 40LP

- Universal Multi-port Memory Controller for RLDRAM2/3, DDR4/3, DDR4 3DS and LPDDR3/2 and LPDDR3/2

- I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

- MIPI D-PHY Universal IP in UMC 40LP