MIPI D-PHY IP

Welcome to the ultimate MIPI D-PHY IP hub! Explore our vast directory of MIPI D-PHY IP

All offers in

MIPI D-PHY IP

Filter

Compare

283

MIPI D-PHY IP

from

24

vendors

(1

-

10)

-

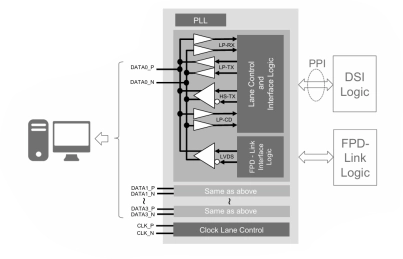

MIPI D-PHY and FPD-Link (LVDS) Combinational Transmitter for TSMC 22nm ULP

- Technology is TSMC 22nm ULP 1p10M.

- Supply voltage can be applied 1.0V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.5Gbps at High-speed mode for MIPI D-PHY Transmitter.

- Data rate of each channel is 609Mbps for FPD-Link(LVDS).

-

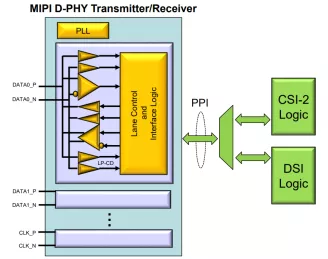

MIPI D-PHY Transmitter/Receiver for DSI/CSI-2 on Samsung 28nm FD-SOI

- Technology is Samsung 28nm FD-SOI 8M (6U1x_2T8x_LB).

- Supply voltage can be applied 1.1V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.5Gbps at High-speed mode.

-

MIPI D-PHY Transmitter/Receiver for TSMC 40nm LP

- Renesas MIPI D-PHY Transmitter/Receiver can be used for analog Transmitter/Receiver of following interface.

- Technology is TSMC 40nm LP 1p6M (4x1z) .

- Supply voltage can be applied 1.1V for core voltage, 1.8V for IO voltage.

-

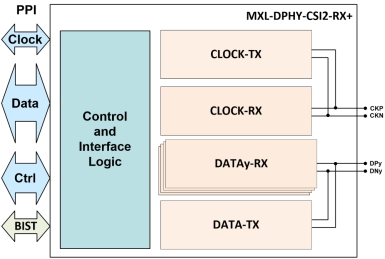

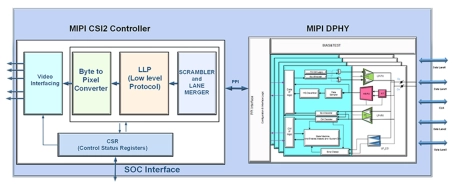

MIPI CSI2 Interface Solution

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

-

MIPI D-PHY TX PHY and DSI controller

- Scalability and Flexibility: Supports multiple data lanes for higher aggregate bandwidth, any of the multiple lanes can be configured into Clock Lane

- High Data Rates: Supports data transmission rates up to 4.5Gbps per lane, allowing for high-resolution displays and smooth refresh rates

- Energy Efficiency: Optimized for low power consumption, making it ideal for battery-powered devices

- Complete Solution: Combines the MIPI D-PHY Transmitter PHY and DSI Controller to make it a one-stop solution

-

MIPI D-PHY℠ v2.5 IP Core

- This Tx/Rx transceiver complies with the MIPI Alliance C-PHY℠ v2.0 and D-PHY℠ v2.5 specifications, with world-class area and power dissipation, and is available for a range of foundry processes.

- This IP delivers 6 Gbps per lane for a max throughput of 24 Gbps in D-PHY℠ mode, and 6 Gsps per trio for a max throughput of 41.04 Gbps in C-PHY℠ mode.

-

MIPI D-PHY v2.1 IP Core

- Compliant to MIPI® Alliance Standard for D-PHY specification Version 2.1

- Supports D-PHY 1.1 synchronous transfer mode at high speed mode with a bit rate of 80-1500 Mb/s without deskew calibration

- Supports DPHY 1.2 for 1500 – 2500 Mb/s with deskew calibration.

-

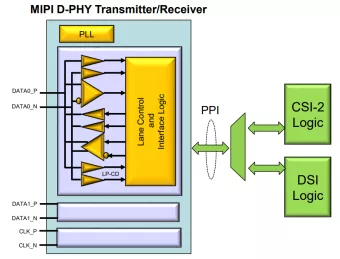

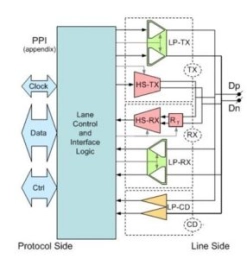

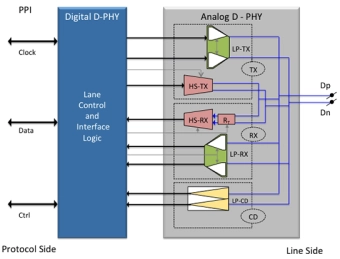

MIPI D-PHY Analog Transceiver IP Core

- The MIPI D-PHY Analog Transceiver IP Core is fully compliant with the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols at speeds up to 1.5Gbps per lane.

- It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

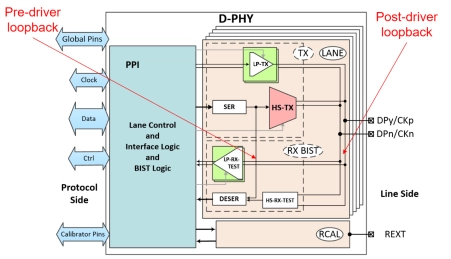

MIPI D-PHY TX+ (Transmitter)

- The MIPI® D-PHY TX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Transmitter.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.

-

MIPI D-PHY RX+ (Receiver) IP

- The MIPI® D-PHY RX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Receiver.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.