I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

The DB-I2C-S-SCL-CLK-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via th…

Overview

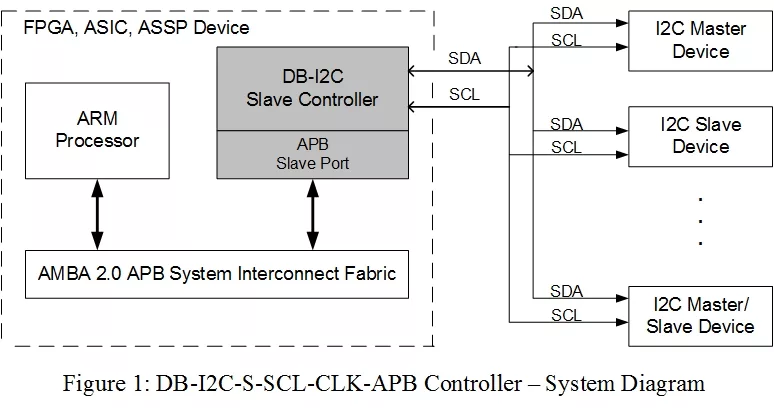

The DB-I2C-S-SCL-CLK-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-SCL-CLK-APB, in the I2C Slave Controller Core managing the I2C protocol & physical layer, contains no free running clock, while interfacing through dual clock FIFOs to the AMBA APB Bus, for a low power, low noise Microprocessor interface to the I2C Bus. The I2C Slave Controller Core runs off the external SCL clock while the APB side off the APB Clock.

The DB-I2C-S-SCL-CLK-APB Controller implements the Slave-Transmit and Slave Receive protocol according to the Philips I2C-Bus Specification, Version 2.1 as well as the updated NXP UM10204 Rev 7 – 1 Oct 2021 Specification.

The DB-I2C-S-SCL-CLK-APB is a member of the vendor DB-I2C Controller IP Core family, which includes I2C Master/Slave, I2C Master-only, and I2C Slave-only configurations.

Figure 1 depicts the system view of the DB-I2C-S-SCL-CLK-APB Controller IP Core embedded within an ASIC, ASSP or FPGA device.

Key features

- Slave I2C Controller Modes:

- Slave – Transmitter

- Slave – Receiver

- Supports four I2C bus speeds:

- Hs-Mode (3.4+ Mb/s)

- Fast Mode Plus (1 Mbit/s)

- Fast Mode (400 Kb/s)

- Standard Mode (100 Kb/s)

- Low power, low noise applications requiring non-free running SCL Clock in the I2C protocol & physical layer logic processing and APB Clock only to interfaceto the Microprocessor.

- Parameterized FIFO memory for off-loading the I2C transfers from the processor:

- Targets embedded processors with higher performance algorithm requirements, by the I2C Controller independently controlling theTransmit or Receive of bytes of information buffered to and from a FIFO.

- I2C compliant features:

- Repeated Start, 7/10-bit addressing

- Enhanced system-level features & integration capabilities:

- CPU Interface via parameterized FIFO with support for APB / AHB / AXI / AXI-lite / Avalon interconnect fabrics

- Enhanced system-level features & integration capabilities (OPTIONAL):

- Direct interface to user Registers within ASIC / ASSP / FPGA device, for Master/Slave transfer across the I2C Bus

- 5 sources of internal interrupts with masking control

- Compliance with AMBA 2.0 and I2C specifications:

- AMBA Specification (Rev 2.0), APB Bus

- Philips/NXP – The I2C-Bus Specification, Version 2.1, January 2000 and UM10204 Rev 7 – 1 Oct 2021

Block Diagram

What’s Included?

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU?

I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU is a I2C / I3C IP core from Digital Blocks, Inc. listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.