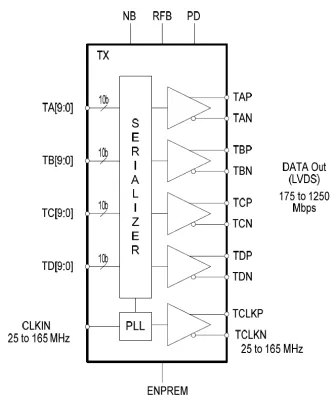

Four Channel (4CH) LVDS Serializer in Samsung 28FDSOI

Overview

The 28FDSOI-LVDS-4CH-TX-1250-PLL is a high performance 4-channel LVDS Serializer implemented using digital CMOS technology. Both the serial and parallel data are organized into four channels. The parallel data is 7/10 bits wide per channel. The input clock is 25MHz to 165MHz. The serializer is highly integrated and requires no external components. It employs optional pre-emphasis to enable transmission over a longer distance while achieving low BER. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

Key Features

- 25-165 MHz clock support

- Up to 1250 Mbps bandwidth/channel

- Up to 5.0 Gbps data throughput

- Low power CMOS design

- LVDS for low EMI

- PLL requires no external components

- Core Voltage & 1.8V dual power supply

- Optional transmit pre-emphasis

- 7/10 bit serial data transmitted per pixel clock per channel

- Rising/falling edge data strobe

- Compatible with TIA/EIA-644 LVDS Standard

Benefits

- Also available as eight-channel (8CH) LVDS Serializer.

Block Diagram

Applications

- Mobile

- Displays

- Cameras/Sensors

- IoT

- VR/AR/MR

- Consumer electronics

- Automotive

Deliverables

- Specifications

- GDSII

- LVS netlist

- LEF file

- IBIS Model

- Verilog Model

- Timing Model

- Integration Guidelines

- RTL

- Documentation

- One year support

Technical Specifications

Foundry, Node

Samsung, 28nm FDSOI

Maturity

Silicon Proven

Availability

Now

Samsung

Pre-Silicon:

28nm

FDS