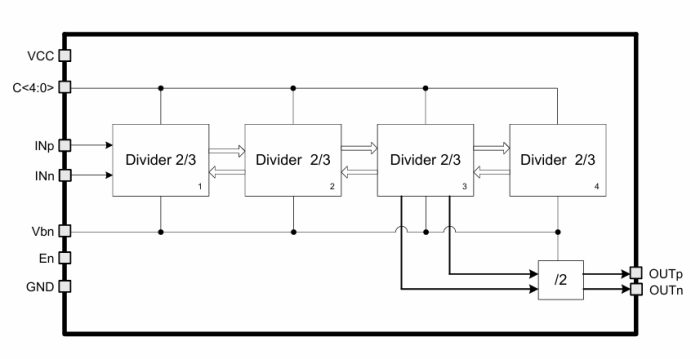

The 5-bit programmable ECL high-frequency divider is a set of serially connected dividers with the varied dividing ratio 2/3 that is able to scale the structure either into minimum dividing ratio decreasing or maximum dividing ratio increasing. The differential circuit has higher noise immunity. An output divider /2 based on D-trigger provides an input signal duty cycle of 0.5.

The block is fabricated AMS BiCMOS 0.35 um technology.

5-bit programmable ECL high-frequency divider

Overview

Key Features

- AMS BiCMOS 0.35 um

- Differential structure

- Dividing ratio is regulated in the range of 16 ...62 with step 2

- Input differential signal frequency up to 1.7 GHz

- Input signal duty cycle is 0.5

- Scalable structure

- Portable to other technologies (upon request)

Block Diagram

Applications

- PLL frequency synthesizer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

5-bit programmable ECL high-frequency divider

Vendor

Vendor Name

Foundry, Node

AMS BiCMOS 0.35 um

Maturity

Silicon proven

Availability

Now