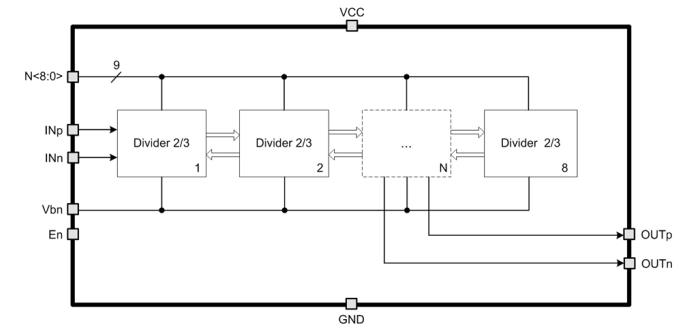

The 9-bit programmable ECL high-frequency divider is a set of serially connected dividers with the varied dividing ratio 2/3 which is able to scale the structure either into minimum dividing ratio decreasing or maximum dividing ratio increasing. The differential circuit has higher noise immunity.

The block is fabricated on AMS BiCMOS 0.35 µm technology.

9-bit programmable ECL HF divider

Overview

Key Features

- AMS BiCMOS 0.35 µm

- Differential structure

- Dividing ratio is regulated in the range of 8...511 with step 1

- Input differential signal frequency up to 1.7 GHz

- Scalable structure

- Portable to other technologies (upon request)

Block Diagram

Applications

- PLL frequency synthesizer

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

9-bit programmable ECL HF divider

Vendor

Vendor Name

Foundry, Node

AMS BiCMOS 0.35 um

Maturity

silicon proven

Availability

Now

Related IPs

- Programmable 9-bit CMOS frequency divider (2…511 dividing ratio)

- Programmable CMOS HF divider (16…4095 dividing ratio)

- Programmable 9-bit CMOS low-frequency divider (5...511 dividing ratio)

- 5-bit programmable ECL high-frequency divider

- 4-bit programmable ECL LF divider (1…15 dividing ratio )

- Programmable CMOS frequency divider (32...16383 dividing ratio)