General Purpose PLL IP

Welcome to the ultimate General Purpose PLL IP hub! Explore our vast directory of General Purpose PLL IP

All offers in

General Purpose PLL IP

Filter

Compare

608

General Purpose PLL IP

from

39

vendors

(1

-

10)

-

High Speed Integer PLL IP

- Up to 4Ghz clock output

- Wide range of multiplicand

- Small physical area

- TEST pin integrated

-

1.7GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 850MHz - 1700 MHz

- Output frequency range : 850MHz -1700 MHz

- Input frequency range : 9.6MHz - 216MHz

-

5GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 2500MHz - 5000 MHz

- Output frequency range : 1250MHz - 2500 MHz

- Input frequency range : 12MHz - 320 MHz

-

1.8GHz SSCG PLL on TSMC 28nm HPC+

- Including Loop-filter

- VCO operating range : 900MHz - 1800 MHz

- Output frequency range : 900MHz-1800 MHz

- Input frequency range : 12MHz - 192MHz

-

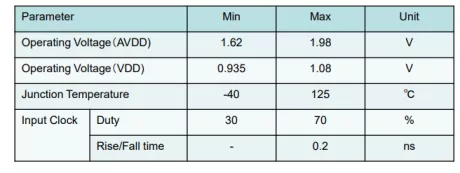

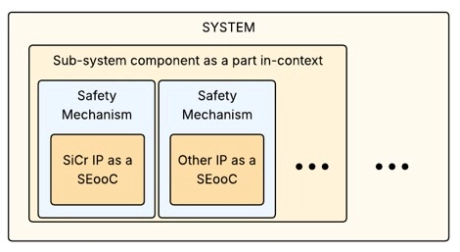

Automotive Grade PLLs, Oscillators, SerDes PMAs, LVDS/CML IP

- TSMC IP9000 Alliance member enabling automotive IP support in TSMC automotive processes

- Automotive Documentation including Safety Manual, FMEDA and DFMEA

- Design reliability report containing EM/IR and Aging analysis

-

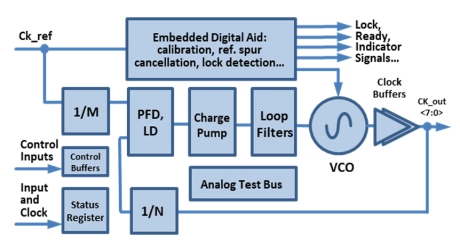

General use, integer-N 4GHz Hybrid Phase Locked Loop on TSMC 28HPC

- This Integer-N Hybrid (Digitally Aided Analog) PLL generates clock signals within broad frequency range.

- Division coefficients of the embedded input and feedback dividers can be set to any integer between 1 and 64 or may be bypassed to save power.

- Higher order dividers and/or pre-scalers are optional.

-

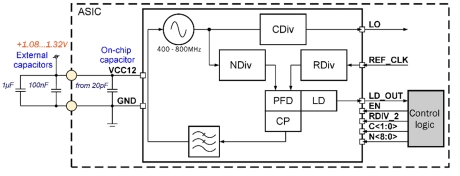

50MHz to 800MHz Integer-N RC Phase-Locked Loop on SMIC 55nm LL

- 055SMIC_PLL_01 forms clock output signal with frequency from 50 to 800MHz.

- It consists of the ring VCO with frequency from 400 to 800MHz, a programmable feedback divider, a low noise digital phase noise detector (PFD), a precision charge pump (CP) with internal loop filter, lock detector (LD) and programmable clock divider to obtain a required output frequency.

- LO output signal is CMOS compatible.

-

ADPLL 2GHz Clock Generator - GLOBALFOUNDRIES 22FDX

- Clock generation based on a Digitally Controlled Oscillator (DCO)

- 800 MHz < = DCO frequency < = 2400 MHz

- Programmable clock frequency dividers for ADPLL loop and clock outputs

- lock-in < 25 us

-

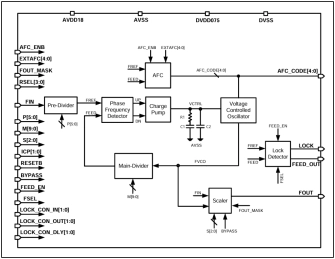

Integer PLL on Samsung 8nm LN08LPP

- PLLF0816X is a 1.8V/0.75V dual supply-voltage phase locked loop (PLL) with a wide-output-frequency-range for frequency synthesis.

- It consists of a phase frequency detector (PFD), a charge pump, a voltage-controlled oscillator (VCO), a 6-bit pre divider, a 10-bit main-divider, a 3-bit scaler, and an automatic frequency control (AFC).

-

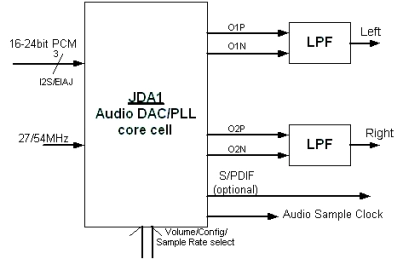

Multi-rate Audio 24-Bit DAC/PLL Core

- Operates from single 27/54MHz clock.

- Ideal for MPEG, AC-3, DVD systems

- Internally generates audio sample clocks

- Multi-sample rates: 32, 44.1, 48 KHz