Perceptia’s DeepSubTM pPLL03 series PLLs are low-cost low-power low-jitter PLLs, for foundry processes from 28 to 180-nm. They are typically used together with the companion IPs pREG01 regulator and pDIV post-scaler. pPLL03 is currently in silicon in the Silterra 180G, ON Semi 180, GlobalFoundries 65LPe, and TSMC 65LP processes.

4-GHz Jitter-optimized low-power digital PLL

Overview

Key Features

- - Jitter below 10-ps

- - Super small: 90 x 90 microns!

- - Very low power: 15-mW

- - Broad frequency range: 4-GHz

- - Fast lock

- - Lock detect

- - Preprogrammed loop filter

- - BIST

- - Scan testable

- - Power-down mode

- - Decoupling caps for lower jitter

- - Available with companion LDO regulator IP

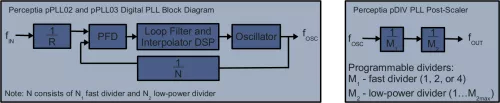

Block Diagram

Deliverables

- The pPLL03 series PLL macros are delivered with:

- - Detailed datasheet including guidance for layout, packaging and production test

- - Characterization report or post-layout corner simulation report

- - LEF abstract for floor planning/chip assembly

- - GDSII layout macrocell

- - Spice/CDL netlist (encrypted format) for LVS

- - DRC / SI verification report

- - Verilog model

- - Timing model (.lib)

- - Test vectors and test guidelines

- - Integration support

Technical Specifications

Short description

4-GHz Jitter-optimized low-power digital PLL

Vendor

Vendor Name

Foundry, Node

28 - 180-nm

Availability

Now

GLOBALFOUNDRIES

Pre-Silicon:

65nm

,

65nm

LP

,

90nm

,

90nm

LP

,

130nm

,

130nm

HP

,

130nm

LP

,

130nm

LV

,

180nm

,

180nm

LL

,

180nm

LL

,

180nm

LP

,

180nm

LP

Silicon Proven: 65nm LPe

Silicon Proven: 65nm LPe

SMIC

Pre-Silicon:

90nm

G

,

90nm

LL

,

110nm

G

,

130nm

G

,

130nm

LL

,

130nm

LV

,

150nm

G

,

150nm

LV

,

160nm

G

,

160nm

LL

,

180nm

EEPROM

,

180nm

G

,

180nm

LL

Silterra

Pre-Silicon:

90nm

,

130nm

Silicon Proven: 180nm

Silicon Proven: 180nm

TSMC

Pre-Silicon:

80nm

,

80nm

GT

,

80nm

HS

,

90nm

G

,

90nm

GOD

,

90nm

GT

,

90nm

LP

,

90nm

zzz

,

110nm

G

,

110nm

LVP

,

130nm

,

130nm

G

,

130nm

LP

,

130nm

LV

,

130nm

LVOD

,

150nm

G

,

150nm

LV

,

160nm

G

,

160nm

LP

,

180nm

,

180nm

E

,

180nm

ELL

,

180nm

FG

,

180nm

G

,

180nm

LP

,

180nm

LV

UMC

Pre-Silicon:

80nm

,

90nm

G

,

90nm

LL

,

90nm

SP

,

110nm

,

130nm

,

150nm

,

162nm

,

180nm